Переход от таблицы истинности к СКНФ и СДНФ

Лабораторная работа №5

ИЗУЧЕНИЕ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ И СХЕМ С ИХ ИСПОЛЬЗОВАНИЕМ

Цель работы

Изучить - основные логические элементы и их таблицы истинности.

- записи таблицы истинности в форме СКНФ и СДНФ

На основе изученных данных реализовать переход таблицы истинности дискретного автомата. Смоделировать в программном средстве и в физической реальности.

Описание лабораторной работы

Логические элементы «И», «ИЛИ», «НЕ», «И-НЕ», «ИЛИ-НЕ»

И их таблицы истинности

Электрическая схема, предназначенная для выполнения какой-либо логической операции с входными данными, называется логическим элементом. Входные данные представляются здесь в виде напряжений различных уровней, и результат логической операции на выходе — также получается в виде напряжения определенного уровня.

Операнды в данном случае подаются в двоичной системе счисления — на вход логического элемента поступают сигналы в форме напряжения высокого или низкого уровня, которые и служат входными данными. Так, напряжение высокого уровня — это логическая единица 1 — обозначает истинное значение операнда, а напряжение низкого уровня 0 — значение ложное. 1 — ИСТИНА, 0 — ЛОЖЬ.

Традиционно логические элементы выпускаются в виде специальных радиодеталей — интегральных микросхем. Логические операции, такие как конъюнкция, дизъюнкция, отрицание и сложение по модулю (И, ИЛИ, НЕ, исключающее ИЛИ) — являются основными операциями, выполняемыми на логических элементах основных типов. Далее рассмотрим каждый из этих типов логических элементов более внимательно.

|

|

|

1.1 Логический элемент «И» - конъюнкция, логическое умножение, AND

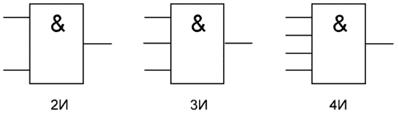

«И» - логический элемент, выполняющий над входными данными операцию конъюнкции или логического умножения. Данный элемент может иметь от 2 до 8 (наиболее распространены в производстве элементы «И» с 2, 3, 4 и 8 входами) входов и один выход.

Условные обозначения логических элементов «И» с разным количеством входов приведены на рисунке.

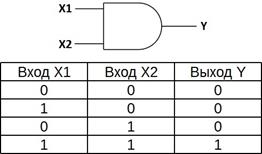

Таблица истинности для элемента 2И показывает, что на выходе элемента будет логическая единица лишь в том случае, если логические единицы будут одновременно на первом входе И на втором входе. В остальных трех возможных случаях на выходе будет ноль.

На западных схемах значок элемента «И» имеет прямую черту на входе и закругление на выходе.

1.2 Логический элемент «ИЛИ» - дизъюнкция, логическое сложение, OR

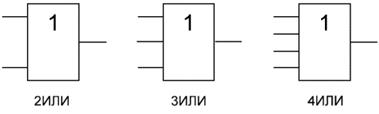

«ИЛИ» - логический элемент, выполняющий над входными данными операцию дизъюнкции или логического сложения. Он также как и элемент «И» выпускается с двумя, тремя, четырьмя и т. д. входами и с одним выходом. Условные обозначения логических элементов «ИЛИ» с различным количеством входов показаны на рисунке.

|

|

|

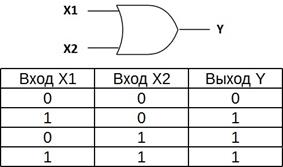

Таблица истинности для элемента «2ИЛИ» показывает, что для появления на выходе логической единицы, достаточно чтобы логическая единица была на первом входе ИЛИ на втором входе. Если логические единицы будут сразу на двух входах, на выходе также будет единица.

На западных схемах значок элемента «ИЛИ» имеет закругление на входе и закругление с заострением на выходе.

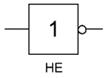

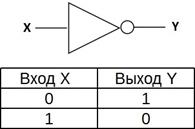

1.3 Логический элемент «НЕ» - отрицание, инвертор, NOT

«НЕ» - логический элемент, выполняющий над входными данными операцию логического отрицания. Данный элемент, имеющий один выход и только один вход, называют еще инвертором, поскольку он на самом деле инвертирует (обращает) входной сигнал. На рисунке приведено условное обозначение логического элемента «НЕ».

Таблица истинности для инвертора показывает, что высокий потенциал на входе даёт низкий потенциал на выходе и наоборот.

На западных схемах значок элемента «НЕ» имеет форму треугольника с кружочком на выходе.

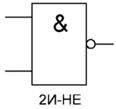

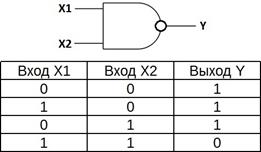

1.4 Логический элемент «И-НЕ» - конъюнкция (логическое умножение) с отрицанием, NAND

|

|

|

«И-НЕ» - логический элемент, выполняющий над входными данными операцию логического сложения, и затем операцию логического отрицания, результат подается на выход. Другими словами, это в принципе элемент «И», дополненный элементом «НЕ». На рисунке приведено условное обозначение логического элемента «2И-НЕ».

Таблица истинности для элемента «И-НЕ» противоположна таблице для элемента «И». Вместо трех нулей и единицы — три единицы и ноль.

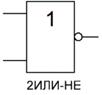

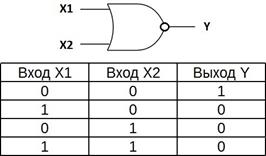

1.5 Логический элемент «ИЛИ-НЕ» - дизъюнкция (логическое сложение) с отрицанием, NOR

«ИЛИ-НЕ» - логический элемент, выполняющий над входными данными операцию логического сложения, и затем операцию логического отрицания, результат подается на выход. Иначе говоря, это элемент «ИЛИ», дополненный элементом «НЕ» - инвертором. На рисунке приведено условное обозначение логического элемента «2ИЛИ-НЕ».

Таблица истинности для элемента «ИЛИ-НЕ» противоположна таблице для элемента «ИЛИ». Высокий потенциал на выходе получается лишь в одном случае - на оба входа подаются одновременно низкие потенциалы.

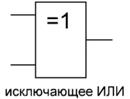

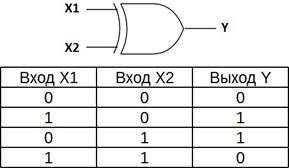

1.6 Логический элемент «исключающее ИЛИ» - сложение по модулю 2, XOR

«Исключающее ИЛИ» - логический элемент, выполняющий над входными данными операцию логического сложения по модулю 2, имеет два входа и один выход. Часто данные элементы применяют в схемах контроля. На рисунке приведено условное обозначение данного элемента.

|

|

|

Изображение в западных схемах — как у «ИЛИ» с дополнительной изогнутой полоской на стороне входа, в отечественной — как «ИЛИ», только вместо «1» будет написано «=1».

Этот логический элемент еще называют «неравнозначность». Высокий уровень напряжения будет на выходе лишь тогда, когда сигналы на входе не равны. Данные элементы логики широко применяются в сумматорах.

Переход от таблицы истинности к СКНФ и СДНФ

Нормальная форма логической формулы существует в двух видах:

А) Конъюнктивная нормальная форма (КНФ) – конъюнкция нескольких дизъюнкций, например,

Б) Дизъюнктивная нормальная форма (ДНФ) – дизъюнкция нескольких конъюнкций, например,

2.1 Совершенная конъюнктивная нормальная форма (СКНФ)

Совершенная конъюнктивная нормальная форма (СКНФ) - это КНФ, удовлетворяющая трем условиям:

- не содержит одинаковых элементарных дизъюнкций;

- ни одна из дизъюнкций не содержит одинаковых переменных;

- каждая элементарная дизъюнкция содержит каждую переменную из входящих в данную КНФ.

Любая булева формула, которая не является тождественно истинной, может быть представлена в СКНФ.

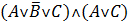

Правило построения СКНФ по таблице истинности

Для каждого набора переменных, при котором функция равна 0, записывается сумма, причем переменные, которые имеют значение 1, берутся с отрицанием.

2.2 Совершенная дизъюнктивная нормальная форма (СДНФ)

Совершенная дизъюнктивная нормальная форма (СДНФ) - это ДНФ, удовлетворяющая трем условиям:

- не содержит одинаковых элементарных конъюнкций;

- ни одна из конъюнкций не содержит одинаковых переменных;

- каждая элементарная конъюнкция содержит каждую переменную из входящих в данную ДНФ, к тому же в одинаковом порядке.

Любая булева формула, которая не является тождественно ложной, может быть представлена в СДНФ, к тому же единственным образом.

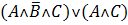

Правило построения СДНФ по таблице истинности

Для каждого набора переменных, при котором функция равна 1, записывается произведение, причем переменные, которые имеют значение 0, берутся с отрицанием.

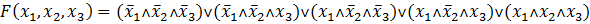

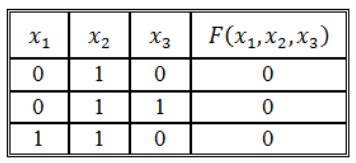

Пример

СДНФ

СКНФ

Примечание: ˅ - Логическое ИЛИ («сложение»);

˄ - Логическое И («умножение»).

3. Таблица истинности дискретного автомата

Дискретный автомат – устройство, предназначенное для преобразования дискретной информации, способное переходить под действием входных сигналов из одного состояния в другое и выдавать выходные сигналы.

| Вариант №1 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 |

| Вариант №2 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 |

| Вариант №3 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

| Вариант №4 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

| Вариант №5 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

| Вариант №6 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 |

| Вариант №7 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 |

| Вариант №8 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

| Вариант №9 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 |

| Вариант №10 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 |

| Вариант №11 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 |

| Вариант №12 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

| Вариант №13 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 |

| Вариант №14 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

| Вариант №15 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 |

| Вариант №16 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 |

| Вариант №17 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 |

| Вариант №18 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

| Вариант №19 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 |

| Вариант №20 | |||

| К1 | К2 | К3 | U1 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

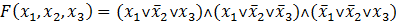

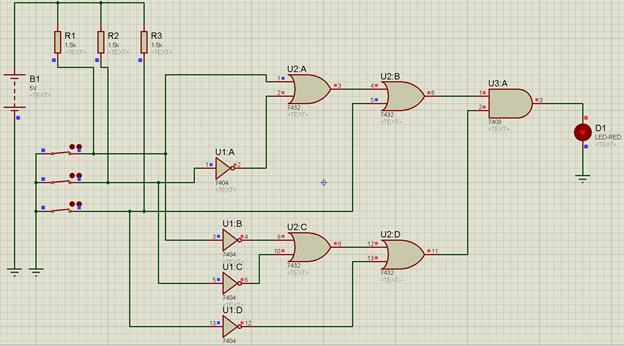

Реализовать дискретный автомат в программном средстве, используя следующие микросхемы: 7408, 7432, 7404

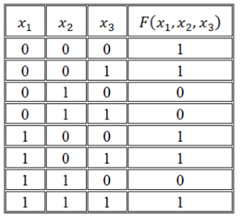

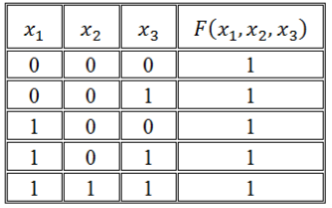

Пример реализации дискретного автомата в программе

Таблица истинности

| К1 | К2 | К3 | U1 |

| 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 |

Рисунок – Комбинация ключей К1=0, К2=1, К3=0

Рисунок – Комбинация ключей К1=0, К2=0, К3=0

Следует учесть, что при данной реализации схемы ключи (переключатели) в замкнутом положении выдают сигнал «0» (синий квадрат), а в разомкнутом – «1» (красный квадрат). Для удобства можно поставить после них логический элемент «НЕ».

4. Реализация дискретного автомата на микросхемах К155ЛЛ1, К555ЛИ3, К155ЛИ1, КМ155ЛН1

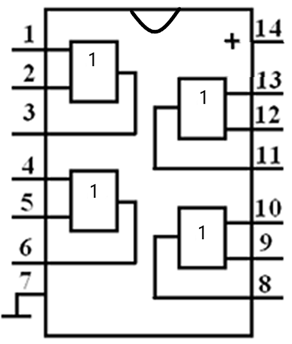

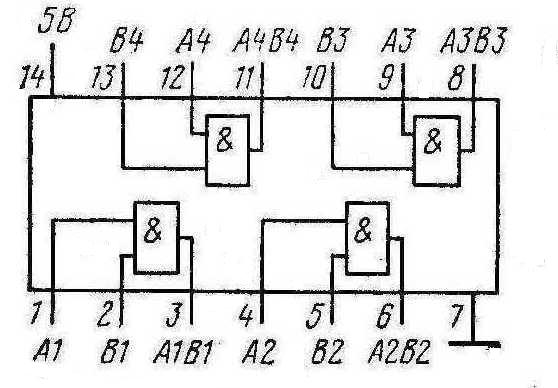

4.1 Микросхема К155ЛИ1

Микросхемы К155ЛИ1, КМ155ЛИ1 (7408) представляет собой четыре логических элемента 2И.

| 1 | Номинальное напряжение питания | 5В + 5% |

| 2 | Выходное напряжение низкого уровня | ≤ 0,4 В |

| 3 | Выходное напряжение высокого уровня | ≥ 2,4 В |

| 4 | Входной ток низкого уровня | ≤ -1,6 мА |

| 5 | Входной ток высокого уровня | ≤ 0,04 мА |

| 6 | Входной пробивной ток | ≤ 1 мА |

| 7 | Ток потребления при низком уровне выходного напряжения | ≤ 33 мА |

| 8 | Ток потребления при высоком уровне выходного напряжения | ≤ 21 мА |

| 9 | Потребляемая статическая мощность на один логический элемент | ≤ 35,4 мВт |

| 10 | Время задержки распространения при включении | ≤ 19 нс |

| 11 | Время задержки распространения при выключении | ≤ 27 нс |

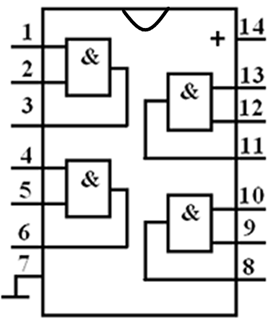

4.2 Микросхема К155ЛЛ1

Микросхемы К155ЛЛ1, КМ155ЛЛ1 (7432) представляют собой четыре логических элемента 2ИЛИ.

| 1 | Номинальное напряжение питания | 5В + 5% |

| 2 | Выходное напряжение низкого уровня | ≤ 0,4 В |

| 3 | Выходное напряжение высокого уровня | ≥ 2,4 В |

| 4 | Входной ток низкого уровня | ≤ -1,6 мА |

| 5 | Входной ток высокого уровня | ≤ 0,04 мА |

| 6 | Входной пробивной ток | ≤ 1 мА |

| 7 | Ток потребления при низком уровне выходного напряжения | ≤ 38 мА |

| 8 | Ток потребления при высоком уровне выходного напряжения | ≤ 22 мА |

| 9 | Потребляемая статическая мощность на один логический элемент | ≤ 39,4 мВт |

| 10 | Время задержки распространения при включении | ≤ 22 нс |

| 11 | Время задержки распространения при выключении | ≤ 15 нс |

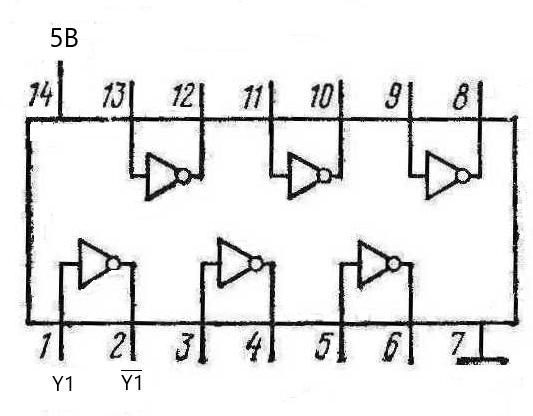

4.3 Микросхема К155ЛН1

Микросхемы К155ЛН1, КМ155ЛН1 (7404) представляет собой шесть логических элементов НЕ.

| 1 | Номинальное напряжение питания | 5В + 5% |

| 2 | Выходное напряжение низкого уровня | ≤ 0,4 В |

| 3 | Выходное напряжение высокого уровня | ≥ 2,4 В |

| 4 | Входной ток низкого уровня | ≤ -1,6 мА |

| 5 | Входной ток высокого уровня | ≤ 0,04 мА |

| 6 | Входной пробивной ток | ≤ 1 мА |

| 7 | Ток потребления при низком уровне выходного напряжения | ≤ 33 мА |

| 8 | Ток потребления при высоком уровне выходного напряжения | ≤ 12 мА |

| 9 | Потребляемая статическая мощность на один логический элемент | ≤ 19,7 мВт |

| 10 | Время задержки распространения при включении | ≤ 15 нс |

| 11 | Время задержки распространения при выключении | ≤ 22 нс |

4.4 Микросхема К155ЛИ3

Микросхемы К155ЛИ1, КМ155ЛИ1 (7408) представляет собой четыре логических элемента 2И

| 1 | Номинальное напряжение питания | 5В + 5% |

| 2 | Выходное напряжение низкого уровня | ≤ 0,4 В |

| 3 | Выходное напряжение высокого уровня | ≥ 2,4 В |

| 4 | Входной ток низкого уровня | ≤ -1,6 мА |

| 5 | Входной ток высокого уровня | ≤ 0,04 мА |

| 6 | Входной пробивной ток | ≤ 1 мА |

| 7 | Ток потребления при низком уровне выходного напряжения | ≤ 33 мА |

| 8 | Ток потребления при высоком уровне выходного напряжения | ≤ 21 мА |

| 9 | Потребляемая статическая мощность на один логический элемент | ≤ 35,4 мВт |

| 10 | Время задержки распространения при включении | ≤ 19 нс |

| 11 | Время задержки распространения при выключении | ≤ 27 нс |

Дата добавления: 2021-05-18; просмотров: 225; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!