Параллельные регистры (регистры параллельной загрузки)

Строятся регистры, как правило, на основе триггеров различных типов. При этом для регистрации n-разрядного двоичного слова

,

,

используется n триггеров, каждый из которых предназначен для регистрации значения цифр строго определенного разряда. Совокупность этих триггеров, объединенных общими цепями управления, и представляет собой регистр.

Параллельный регистр используется для одновременного запоминания многоразрядных двоичных (или недвоичных) чисел.

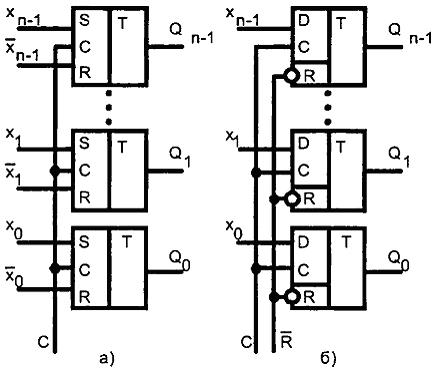

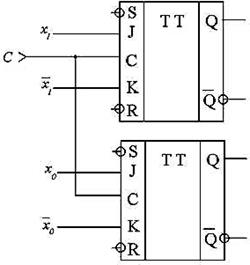

Название параллельного регистра связано с тем, что входы и выходы всех триггеров в этой схеме используются независимо (рисунок 16.1). Поэтому триггеры, соответствующие разным разрядам не связаны между собой. Входы синхронизации всех триггеров соединены параллельно. Это приводит к тому, что информация вних записывается одновременно.

Рисунок 16.1 – Функциональные схемы параллельных регистров

С использованием: а) – RS -триггеров; б) – D -триггеров

В параллельных регистрахдля обеспечения одновременной записи и считывания всех разрядов кода числа используются однотипные триггеры и логические схемы. Рассмотрим принцип построения таких схем.

Различают два способа записи и считывания информации: парафазный (двухфазный)и однофазный.

Двухфазный способ (см. рисунок 16.1 а) отличается тем, что информация к триггеру i-го разряда регистра подводится по двум проводам: по одному поступает –  , а по другому –

, а по другому –  .

.

|

|

|

При однофазном способе записи (см. рисунок 16.1 б) информация о двоичном символе  , который надо записать в триггер i-го разряда регистра, подводится к нему по одному проводу.

, который надо записать в триггер i-го разряда регистра, подводится к нему по одному проводу.

Объединяя функциональные схемы i-х разрядов по входу синхронизации можно получить параллельный регистр любого числа разрядов.

Подавая на входы RS-триггеров парафазные сигналы (см. рисунок 16.1 а), в регистр записывается двоичный код. При  активный сигнал воздействует на вход

активный сигнал воздействует на вход  и триггер устанавливается в единичное состояние. При

и триггер устанавливается в единичное состояние. При  , логическая единица поступает на вход

, логическая единица поступает на вход  и триггер устанавливается в состояние 0. Следовательно, состояния регистров определяется поступающими на входы сигналами. Запись входного кода происходит во время прихода синхроимпульса на вход С.

и триггер устанавливается в состояние 0. Следовательно, состояния регистров определяется поступающими на входы сигналами. Запись входного кода происходит во время прихода синхроимпульса на вход С.

Если для записи в данном регистре используется только прямой или только обратный входной код, то запись информации выполняется за два такта синхронизации. По первому такту необходимо сбросить или установить все триггеры регистра подачей на соответствующие входы активного логического уровня, а по второму – записать в регистр новую информацию.

На рисунке (см. рисунок 16.1 б) параллельный однотактный регистр построен на D-тригтерах с однофазным входом. В таком регистре при уровне логической 1 на входе  все триггеры устанавливаются в состояния, определяемые действующим на D-входах входными сигналами. Для записи информации необходим только один импульс синхронизации

все триггеры устанавливаются в состояния, определяемые действующим на D-входах входными сигналами. Для записи информации необходим только один импульс синхронизации  . Дополнительный вход

. Дополнительный вход  начальной установки переводит все триггеры в нулевые состояния одним управляющим импульсом.

начальной установки переводит все триггеры в нулевые состояния одним управляющим импульсом.

|

|

|

Параллельные регистры могут иметь дополнительно вспомогательные комбинационные схемы, которые расширяют функциональные возможности. Они используются для установки начального состояния, режима приема, хранения либо выдачи информации, реализуют запись с двух направлений и т. д. В этом случае регистр имеет соответствующие входы.

На рисунке 16.2 показана реализация параллельного двухразрядного регистра на универсальных JK триггерах. В данной схеме используется парафазный способ представления записываемых данных. Выводы  и

и  триггеров могут использоваться для начальной установки регистра в заданное состояние. При реализации параллельного регистра на дискретных триггерах выходной сигнал можно по выбору считывать как в прямом, так и инверсном виде.

триггеров могут использоваться для начальной установки регистра в заданное состояние. При реализации параллельного регистра на дискретных триггерах выходной сигнал можно по выбору считывать как в прямом, так и инверсном виде.

Рисунок 16.2 – Двухразрядный параллельный регистр на JK -триггерах

|

|

|

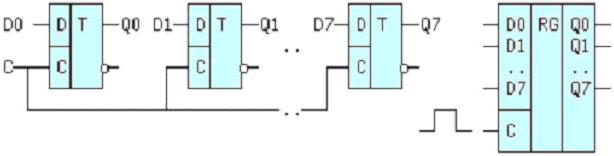

2.2.Регистр-защелка на D-триггерах

Регистры с параллельной записью называются, также регистрами памяти. В них могут использоваться, как прозрачные"защелки", так и триггеры с динамическим управлением. На рисунке 16.3 приведена схема 8-ми разрядного регистра памяти с общим входом управления записью информацией и ее УГО. Высокий уровень на входе C переписывает информацию с входа на выход (Qi=Di), а низкий уровень – защелкивает данные.

Рисунок 16.3 – Схема 8-ми разрядного регистра памяти

Регистры обычно строятся на основе D -триггеров. При этом для построения регистров могут использоваться как динамические, так и статические D -триггеры (триггеры-защелки).

При использовании регистров со статическим входом тактирования удается достичь максимального быстродействия цифровой схемы, однако при этом следует соблюдать осторожность, т. к. при воздействии на вход синхронизации единичного потенциала логические сигналы с входов такого регистра будут свободно проходить на его выходы. Поэтому при использовании статических регистров в схеме цифрового устройства обычно применяется двухтактная синхронизация.

|

|

|

Количество триггеров в составе регистра определяет его разрядность. В качестве отдельных микросхем обычно используются четырех- или восьмиразрядные регистры.

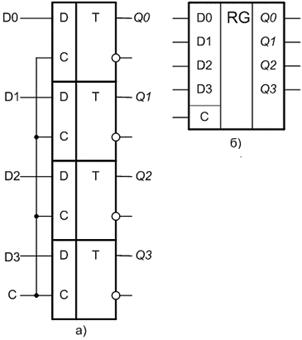

Регистр-защелка.Простейший регистр представляет собой параллельное соединение нескольких триггеров (рисунок 16.4 а). УГО регистра-защелки приведено на рисунке 16.4 б.

Рисунок 16.4 – Четырёхразрядный параллельный регистр-"защелка" с прямыми выходами: а – функциональная схема; б – УГО

В УГО параллельного регистра возле каждого входа D указывается степень двоичного разряда, который должен быть запомнен в этом триггере (разряде) регистра. Точно таким же образом обозначаются и выходы регистра. То, что микросхема является регистром, указывается в центральном поле УГО символами RG. Инверсные выходы триггеров на УГО не показаны. В реально выпускающихся микросхемах параллельных регистров инверсные выходы триггеров обычно не выводятся наружу для экономии количества выводов корпуса.

Следует отметить, что назначение разрядов в параллельном регистре является условным. Если по каким-либо причинам (например, с точки зрения разводки печатной платы) удобно изменить нумерацию разрядов, то это можно свободно осуществить. При перенумерации входов нужно не забыть, точно таким же образом изменить номера его выходов.

Если регистр построен на триггерах-защелках, то его называют регистр- "защелка".

В схеме параллельного регистра для уменьшения входного тока вывода синхронизации С на этом входе применяется усилитель. В качестве подобного усилителя обычно используется логический инвертор (стробирующий вход STB).

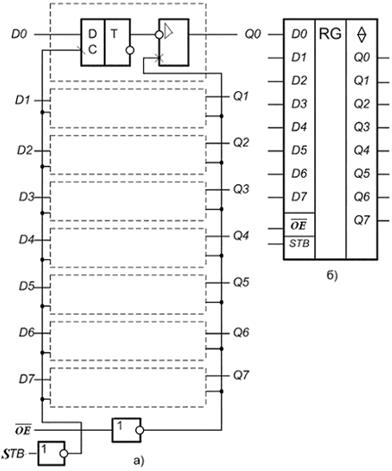

Как правило, в состав ИС регистра входят буферные усилители (регистры) и элементы управления (выходной вентиль), например как показано на рисунке 16.5 а. Здесь изображена функциональная схема 8-разрядного D-регистра-защелки КР580ИР82. Его УГО представлено на рисунке 16.5 б.

Рисунок 16.5 – Восьмиразрядный регистр-"защелка" КР580ВМ80А (КР580ИР82): а – функциональная схема; б – УГО

На его выходе могут быть три состояниями:

- первое – логический 0;

- второе – логическая 1;

- третьим состоянием называется состояние выходов ИС, при котором они отключены и от источника питания, и от общей точки. Другие названия этого состояния – состояние высокого сопротивления, высокоимпедансное состояние, Z-состояние.

Достигается это третье состояние специальным схемным решением в выходной части логических элементов, когда выходные транзисторы логических элементов заперты и не подают на выход ни напряжения питания, ни потенциала земли (не 0 и не 1).

Регистр КР580ИР82 состоит из 8 функциональных блоков (см. рисунок 16.5 а). В каждый из них входит:

- D-триггер-защелка с записью по заднему фронту;

- мощный выходной вентиль на 3 состояния;

- STB – стробирующий вход;

-  – сигнал разрешения передачи.Это сигнал, управляющий третьим состоянием: 1) Если

– сигнал разрешения передачи.Это сигнал, управляющий третьим состоянием: 1) Если  , то происходит передача информации со входов

, то происходит передача информации со входов

на соответствующие выходы

на соответствующие выходы  ;

;

2) Если же  , все выходы

, все выходы  переводятся в третье состояние.

переводятся в третье состояние.

При  и

и  . ИС работает в режиме шинного формирователя – информация со входов

. ИС работает в режиме шинного формирователя – информация со входов  передается на выходы

передается на выходы  в неизменном виде.

в неизменном виде.

При подаче на STB заднего фронта сигнала происходит "защелкивание" передаваемой информации в триггерах, то есть там запоминается то, что было на момент подачи  .

.

Пока  , буферный регистр будет хранить эту информацию, независимо от информации на D-входах.

, буферный регистр будет хранить эту информацию, независимо от информации на D-входах.

При подаче переднего фронта  при сохранении

при сохранении  состояние выходов

состояние выходов  будет изменяться в соответствии с изменением на соответствующих входах

будет изменяться в соответствии с изменением на соответствующих входах  .

.

Если же  , то все выходные усилители переводятся в третье состояние. При этом, независимо от состояния входов, все выходы регистра

, то все выходные усилители переводятся в третье состояние. При этом, независимо от состояния входов, все выходы регистра  переводятся в третье состояние.

переводятся в третье состояние.

Все выводы регистра могут иметь активный нулевой уровень, что отображается на УГО в виде инверсных сигналов и обозначений выводов.

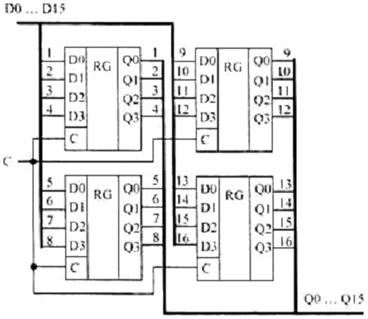

При решении практических задач часто требуется разрядность параллельных регистров, большая восьми. В таком случае можно увеличивать разрядность регистров параллельным соединением готовых микросхем. Принципиальная схема параллельного соединения четырех регистров приведена на рисунке 16.6.

Рисунок 16.6 – Увеличение разрядности параллельного регистра

В схеме, приведенной на рисунке 16.6, реализован 16-разрядный параллельный регистр.

Сдвигающие регистры

Существует множество разновидностей регистров, например, сдвиговые регистры, в которых триггеры соединены между собой таким образом, что передают информацию последовательно от одного триггера к другому.

В последовательных регистрах запись и считывание чисел производится в последовательном коде, т. е. разряд за разрядом, начиная со старших (или младших).

Последовательные регистры могут иметь цепи параллельной записи информации в регистр и выдачи ее из регистра. С помощью таких регистров осуществляется преобразование последовательных кодов в параллельные и наоборот.

Для сохранения считываемой из последовательного регистра информации, его выход с помощью ЛЭ соединяют со входом. В этом случае записанная в регистре информация циркулирует в нем. Такой регистр называется закольцованным.

Последовательные (сдвигающие) регистрыпредставляют собою цепочку разрядных схем, связанных цепями переноса.

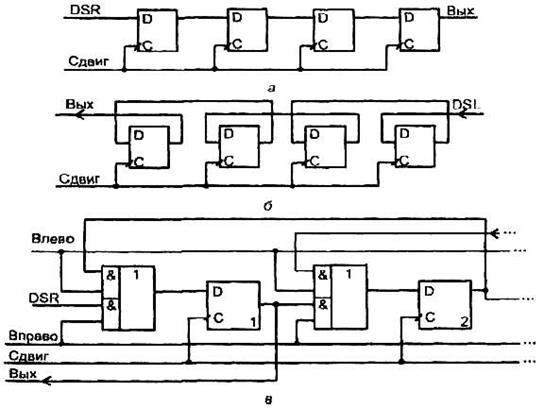

В однотактных регистрах со сдвигом на один разряд вправо (рисунок 16.7 а)слово сдвигается при поступлении синхросигнала. Вход и выход последовательные (DSR – Data Serial Right). На рисунке 16.7 бпоказана схема регистра со сдвигом влево (вход данных DSL – Data Serial Left), а на рисунке 16.7 виллюстрируется принцип построения реверсивного регистра, в котором имеются связи триггеров с обоими соседними разрядами, но соответствующими сигналами разрешается работа только одних из этих связей (команды "влево" и "вправо" одновременно не подаются).

Рисунок 16.7 – Схемы регистров сдвига:

Дата добавления: 2021-05-18; просмотров: 1395; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!