Использование стандартных интегральных схем

Логические интегральные элементы широко используют при построении схем совпадений. Схемы совпадений с разрешающим временем, лежащим в наносекундном диапазоне, выполняют обычно на элементах транзисторно-транзисторной логики (ТТЛ) и логики с эмиттерными связями (ЭСТЛ). Как правило, эти элементы рассчитаны на стандартизованные сигналы, поэтому в схемы совпадений необходимо вводить формирователи.

В качестве примера на рис. 1, а приведена схема совпадений, выполненная на логическом элементе И типа К1ЛБ376. Сформированные отрицательные сигналы поступают на базы эмиттерно-связанных транзисторов  , входящих в левое плечо дифференциального каскада, в правой плече которого стоит

, входящих в левое плечо дифференциального каскада, в правой плече которого стоит  . Через нагрузку левого плеча Rл течет ток до тех пор, пока открыт хотя бы один из транзисторов

. Через нагрузку левого плеча Rл течет ток до тех пор, пока открыт хотя бы один из транзисторов  При совпадении сигналов на всех входах ток через

При совпадении сигналов на всех входах ток через  прекращается; с выхода схемы снимается отрицательный импульс совпадений. Включенный на выходе эмиттерный повторитель повышает нагрузочную способность схемы. Минимальное разрешающее время этой схемы по совпадениям 5 НЕ.

прекращается; с выхода схемы снимается отрицательный импульс совпадений. Включенный на выходе эмиттерный повторитель повышает нагрузочную способность схемы. Минимальное разрешающее время этой схемы по совпадениям 5 НЕ.

В схему совпадений на логическом элементе И легко ввести канал антисовпадений (рис. 1,6). Для этого один из эмиттерно-связанных транзисторов смещается напряжением - Е, а поступающий на базу этого транзистора сигнал инвертируется схемой НЕ. При одновременном поступлении сигналов на входы 1-4 на выходе схемы возникает сигнал совпадений. Если в это время есть-сигнал антисовпадений, то он благодаря инвертору держит открытым подключенный к каналу транзистор н сигнал совпадений не возникает. Для четкой работы схемы необходимо, чтобы поступающий по входу АС сигнал появлялся' немного раньше, а исчезал немного позже сигналов, приходящих по каналам совпадений. Это обеспечивается формирователями и задержками.

|

|

|

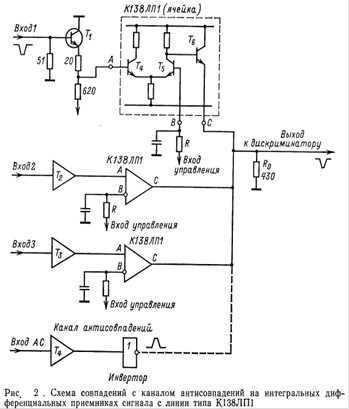

Быстродействующие управляемые схемы совпадений удобно выполнять на-элементах ЭСТЛ, в частности на дифференциальных приемниках сигнала с линии. Такой элемент К138ЛП1 (рис. 2) имеет дифференциальный каскад  ,

,  и выходной эмиттерный повторитель

и выходной эмиттерный повторитель  . В схеме совпадений импульсы совпадений поступают через согласующие уровни транзисторов

. В схеме совпадений импульсы совпадений поступают через согласующие уровни транзисторов  на одноименные входы А всех элементов К138ЛП1, на вторые входы В поступают управляющие уровни. Совпадения выделяются на общем резисторе

на одноименные входы А всех элементов К138ЛП1, на вторые входы В поступают управляющие уровни. Совпадения выделяются на общем резисторе  , к которому подключены эмиттерные выходы всех элементов. В случае частичных совпадений входной уровень практически не изменяется, так как он поддерживается током повторителей, на которые сигналы не поступают.

, к которому подключены эмиттерные выходы всех элементов. В случае частичных совпадений входной уровень практически не изменяется, так как он поддерживается током повторителей, на которые сигналы не поступают.

Данную схему легко дополнить каналом антисовпадений (см. на рис. 2). В канале имеется инвертор, токовый выход которого также соединяется с общим резистором  . При поступлении сигнала на, вход антисовпадений АС и одновременном приходе сигналов на остальные входы совпадение регистрироваться не будет, так как на

. При поступлении сигнала на, вход антисовпадений АС и одновременном приходе сигналов на остальные входы совпадение регистрироваться не будет, так как на  поступает положительный импульс инвертора.

поступает положительный импульс инвертора.

|

|

|

Разрешающее время по совпадениям у схем на элементах с эмиттерно-связанной логикой в основном определяется длительностью сформированных импульсов и обычно составляет несколько наносекунд.

Разобранные примеры показывают, что быстродействующие интегральные элементы позволяют выполнять схемы совпадений с такими же высокими параметрами, как и на дискретных элементах. Преимущества интегральных схем особенно проявляются при создании сложных устройств совпадений и годоскопических систем с расширенной логической структурой. Интегральные схемы также позволяют создавать цифровые мажоритарные схемы с высокой кратностью совпадений.

Дата добавления: 2021-02-10; просмотров: 81; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!