УЧЕБНЫЕ ЗАДАНИЯ И МЕТОДИЧЕСКИЕ УКАЗАНИЯ

Лабораторная работа 03 ( Lr03)

РЕГИСТРЫ

ЦЕЛЬ РАБОТЫ

Ознакомление с устройством и функционированием регистров и регистровой памяти; испытание интегрального универсального регистра сдвига.

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ И РАСЧЁТНЫЕ ФОРМУЛЫ

КЛАССИФИКАЦИЯ РЕГИСТРОВ

Регистр - это последовательностное устройство,предназначенное для записи, хранения и (или) сдвига информации, которая поступает и хранится в регистре в виде п-разрядных двоичных чисел. В общем случае регистр может выдавать информацию в последовательной или параллельной форме, преобразовывать прямой код числа в обратный (когда единицы заменяются нулями, а нули - единицами), и наоборот, а также выполнять логическое сложение и логическое умножение двоичных чисел.

В зависимости от способа ввода и вывода разрядов числа различают регистры параллельные, последовательные и параллельно-последовательные. В параллельном регистре ввод и вывод всех разрядов кодового числа осуществляется одновременно, в последовательном - разряды числа вводятся и выводятся последовательно, а в параллельно-последовательном регистре ввод числа производится в параллельной форме, а вывод - в последовательной, и наоборот. Преобразование параллельного кода в последовательный и наоборот – очень актуальная задача, так как передача цифровой информации в сетях передачи данных осуществляется в последовательном коде, а обработка её в микропроцессорах вычислительных устройств – в параллельном.

|

|

|

Регистр, в котором можно осуществить сдвиг числа, называют сдвигающим (сдвиговым), причем сдвиг может быть или в одну сторону (в сторону младшего разряда - прямой (правый) сдвиг, или в сторону старшего разряда – обратный (левый) сдвиг, или в обе стороны (реверсивный сдвигающий регистр). В этом смысле последовательный и параллельно-последовательный регистры относят к сдвиговым.

Регистр, в котором можно осуществить сдвиг числа, называют сдвигающим (сдвиговым), причем сдвиг может быть или в одну сторону (в сторону младшего разряда - прямой (правый) сдвиг, или в сторону старшего разряда – обратный (левый) сдвиг, или в обе стороны (реверсивный сдвигающий регистр). В этом смысле последовательный и параллельно-последовательный регистры относят к сдвиговым.

Отечественная промышленность выпускает многие типы регистров в виде микросхем. В качестве примера на рис. 03.1 приведено изображение четырехразрядного регистра (микросхема серии К155). При V2 = 0 разряды числа вводят последовательно в регистр через вход V1; синхроимпульсы, поступающие на вход С1, обеспечивают сдвиг вправо разрядов числа; регистр работает как сдвигающий. В микросхеме (см. рис. 03.1) предусмотрен также параллельный ввод всех разрядов числа по синхроимпульсу на входе С2 с входов D1, …, D4 при V2 = 1. В данном случае регистр работает как параллельный.

Если выводы последнего триггера сдвигающего регистра соединить с входами первого, то получится кольцевой регистр сдвига, называемый кольцевым счётчиком. Его коэффициент пересчёта равен числу разрядов п: единица, записанная в один из разрядов, периодически появляется на выходе счётчика после того, как пройдут п сдвигающих синхроимпульсов.

|

|

|

2. ПАРАЛЛЕЛЬНЫЙ РЕГИСТР НА RS-ТРИГГЕРАХ

Любой регистр состоит из связанных между собой триггеров с динамическим или статическим управлением и логических элементов, причем количество триггеров равно количеству разрядов в записываемом числе. Синтез регистра сводится к выбору типа триггеров и логических элементов И, НЕ, ИЛИ для реализации заданных операций.

|

Рассмотрим работу параллельного регистра на RS-триггерах (рис. 03.2). Ввод (запись) числа осуществляется в два такта. Во избежание ошибочной записи числá х1х2…х п в первом такте все триггеры регистра обнуляются. Для этого на шину "0" подается логический 0. Во втором такте по сигналу 1 на шине "П" ("Приём") через конъюнкторы одновременно записывается в соответствующие разряды регистра двоичное число х1х2…х п. Вывод (считывание) числа у1у2…у п в прямом коде происходит по сигналу 1 на шине "В пр", а в обратном - по сигналу 1 на шине "В обр".

|

Объединив в одной микросхеме несколько регистров и добавив на входе дешифратор DCW, а на выходе мультиплексор MS, получают регистровую (сверхоперативную) память (рис. 03.3). Входы D i четырёх или восьми регистров, как правило, 4-разрядных, подключают к общей входной шине данных DIN. Вход загрузки требуемого регистра выбирается дешифратором записи DCW на основании поступающего на его вход адреса записи WA, т. е. кода номера загружаемого регистра. Запись данных, присутствующих на шине DIN, происходит в момент поступления сигнала разрешения записи WE.

|

|

|

Выходы регистров мультиплексором MS подключаются к выходной шине DOUT. Номер регистра, с которого происходит чтение, определяется посредством кода адреса чтения RA. Разрешение выдачи данных в шину DOUT происходит по сигналу RE. Поскольку дешифрация адреса записи и адреса чтения производится двумя независимыми узлами, имеющими автономные адресные входы WA и RA, в регистровую память можно одновременно записывать бинарное число в один из регистров и считывать число из другого. Описанная структура использована в кристаллах отечественных микросхем К155РП1, ИР11 и ИР12 серий К561 и К564.

Микросхемы регистровой памяти легко наращиваются по разрядности и допускают наращивание по числу регистров. Они разработаны для построения блоков регистров общего назначения (РОН), предназначенных для временного хранения исходных данных и промежуточных результатов расчёта в микропроцессорах.

|

|

|

УЧЕБНЫЕ ЗАДАНИЯ И МЕТОДИЧЕСКИЕ УКАЗАНИЯ

К ИХ ВЫПОЛНЕНИЮ

Задание 1. Запустить лабораторный комплекс среду CIRCUIT SIMULATOR. Собрать на рабочем поле среды CIRCUIT SIMULATOR схему для испытания регистра сдвига PISO, «параллельный вход, последовательный выход» (рис. 03.4) и установить в диалоговых окнах компонентов их параметры или режимы работы. Скопировать схему (рис. 03.4) на страницу отчёта.

Рис. 03.4

Сдвиговый регистр параллельного входа – последовательного выхода (PISO) это регистр, который допускает параллельный ввод и производит последовательный выход, известен как сдвиговый регистр Parallel In-Serial Out (PISO) . В эксперименте используется схема 8-битного регистра сдвига PISO.

Эта схема состоит из восьми D-триггеров, которые подключены каскадно. Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронны друг с другом, поскольку к каждому из них применяется один и тот же тактовый сигнал.

Задание 2. Составить схему исследования параллельного регистра сдвига, заполнив ячейки памяти генератора слова G2 на основе трех правил функционирования.

Заполнините таблицу 03.1 истинности для 3 случаев для двух положений переключателя S1’

Т а б л и ц а 03.1

| Такт | 1 | 2 | 3 | 4 | 5 | 6 | 76 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| Кан1 | ||||||||||||||||

| Кан2 | ||||||||||||||||

| Кан3 | ||||||||||||||||

| Кан4 | ||||||||||||||||

| Кан5 | ||||||||||||||||

| Кан6 | ||||||||||||||||

| Кан7 | ||||||||||||||||

| Кан8 | ||||||||||||||||

| Кан9 | ||||||||||||||||

| Кан10 |

Запустить программу моделирования параллельного регистра, скопировать в отчёт временные диаграммы сигналов (см. рис. 03.6).

Ввод (запись) и вывод (считывание) информации производится параллельным кодом. Ввод обеспечивается тактовым импульсом, с приходом очередного тактового импульса записанная информация обновляется. Считывание информации происходит в прямом коде в интервале между синхроимпульсами, когда триггеры находятся в режиме хранения.

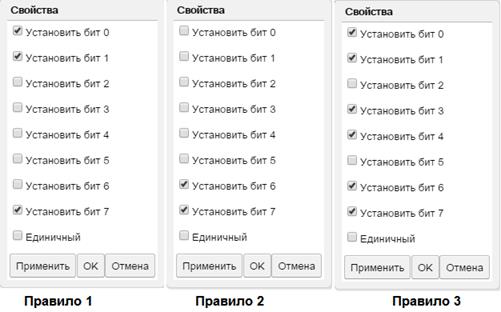

В качестве примера на рис. 03.5 приведена запись 8-разрядных кодовых комбинаций в ячейки памяти генератора G2.

Рис. 03.5

Рис. 03.6

Задание 3. Собрать на рабочем поле среды CIRCUIT SIMULATOR схему для испытания регистра сдвига SIPO (рис. 03.7) и установить в диалоговых окнах компонентов их параметры или режимы работы. Скопировать схему (рис. 03.7) в отчёт.

Рис. 03.7

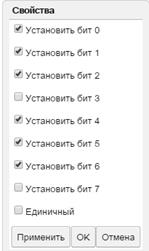

Составить схему исследования параллельного регистра сдвига, заполнив ячейки памяти генератора слова G2 на основе следующего правилафункционирования.

Рис. 03.8

Заполнините таблицу 03.21 истинности для двух положений переключателя S1’

Т а б л и ц а 03.2

| Такт | 1 | 2 | 3 | 4 | 5 | 6 | 76 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| Кан1 | ||||||||||||||||

| Кан2 | ||||||||||||||||

| Кан3 | ||||||||||||||||

| Кан4 | ||||||||||||||||

| Кан5 | ||||||||||||||||

| Кан6 | ||||||||||||||||

| Кан7 | ||||||||||||||||

| Кан8 | ||||||||||||||||

| Кан9 |

Запустить программу моделирования, скопировать в отчёт временные диаграммы сигналов (см. рис. 03.8).

Рис. 03.8

Задание 4. Составить план исследования последовательного регистра 74НС194_4 V, заполнив ячейки памяти генератора XWG1 произвольными (или по заданию преподавателя) 4-разрядными кодовыми комбинациями, вводимыми последовательно сперва в регистр А, а затем в регистр D.

СОДЕРЖАНИЕ ОТЧЁТА

1. Наименование и цель работы.

2. Перечень приборов, использованных в экспериментах, с их краткими характеристиками.

3. Изображения электрических схем для испытания параллельного и последовательного регистров.

4. Копии временных диаграмм, отображающих работу исследуемых регистров.

5. Выводы по работе.

6. Сохранить файл схемы согласно «введению к проведению лабораторных работ онлайн»

https://vk.com/doc7132395_540132563?hash=44bcb8a3d7b3deed73&dl=ab88a9fbed29aa78e0

7. Переслать отчет и файлы схем на проверку mrradik@mail.ru

ТЕСТОВЫЕ ЗАДАНИЯ К РАБОТЕ

1. Укажите функции, которые в общем случае может выполнять регистр.

Обнуление (очистку) хранимой информации, запись входной информации в последовательном или в параллельном коде

Суммирование по модулю 2 всех разрядов бинарных чисел с целью выяснения чётности числа

Сравнение двух бинарных чисел одинаковой разрядности с целью определения их равенства или неравенства

Преобразование информации путём её сдвига под воздействием тактовых импульсов

Хранение информации, её сдвиг вправо и влево, выдачу хранимой информации в последовательном или в параллельном коде

Преобразование десятичных чисел в двоичные или в двоично-десятичные

2. В параллельном регистре с приходом каждого тактового импульса информация на выходах поразрядно сдвигается в направлении от выхода QD к выходу QА. Укажите, как называют такой регистр?

Регистр прямого сдвига Регистр обратного сдвига

Реверсивный регистр

Регистр хранения.

3. Укажите, какие регистры выполняют со статическим управлением?

Последовательные

Параллельные

Последовательно-параллельные Параллельно-последовательные

4. Укажите, при каких уровнях сигналов на управляющих входах S0 и S1 информационные входы реверсивного регистра 74НС194_4V недоступны?

S0 = 0, S1 = 0

S0 = 0, S1 = 1

S0 = 1, S1 = 0

S0 = 1, S1 = 1

5. Укажите, в какой разряд вводится информация последовательного регистра 74НС194_4V при S0 = 1, S1 = 0 на управляющих входах и сигналах SR = 1 и  = 1?

= 1?

В разряд D

В разряд С

В разряд В

В разряд А

.

6. Укажите, при каких уровнях управляющих сигналов S0 и S1 разрешена запись информации в параллельный регистр 74НС194_4V?

S0 = 0, S1 = 0

S0 = 0, S1 = 1

S0 = 1, S1 = 0

S0 = 1, S1 = 1

7. Укажите, разрешено ли последовательное перемещение сигналов в триггерной подсистеме параллельного регистра 74НС194_4V во время записи информации?

7. Укажите, разрешено ли последовательное перемещение сигналов в триггерной подсистеме параллельного регистра 74НС194_4V во время записи информации?

Да

Нет

8. Укажите, сколько входов имеет последовательный регистр с динамическим управлением?

Один информационный вход

Два: один информационный вход и вход для тактовых импульсов (импульсов сдвига)

Три: один информационный, вход для тактовых импульсов и установочный вход

Четыре: два информационных входа, вход для тактовых импульсов и установочный вход

9. Укажите, чем отличается динамическое управление регистрами от статического управления?

Принципиальных отличий нет: сигналы, поступающие на информационные входы всех модификаций регистров, действуют в момент их поступления

У регистров с динамическим управлением сигналы на информационных входах должны оставаться неизменными на всём интервале действия активного логического сигнала синхронизации (С = 1)

При динамическом управлении запоминание сигналов, действующих на информационных входах регистра, происходит во входных ёмкостях МДП-транзисторов в момент изменения значения сигнала на входе синхронизации, а в статических регистрах, построенных, например на RS-триггерах, сигналы действуют в момент их поступления на информационные входы

Дата добавления: 2020-04-25; просмотров: 338; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!