ОПЕРАТОР ОЖИДАНИЯ WATI ЯЗЫКА VHDL

Операторы ожидания позволяют управлять моментами времени, в которые параллельные операторы будут реагировать на изменение сигналов. Операторы ожидания имеет следующий синтаксис:

wait [ on signal_jname {,...} ]

[until boolean_expression]

[for time_expression];

Оператор wait позволяет приостанавливать выполнение параллельного оператора в модели и программно задавать условия, при которых его выполнение может быть возобновлено.

Выполнение оператора wait приводит к приостановке выполнения параллельного оператора на некоторое время или до выполнения некоторого условия. Как только заданные условия будут выполнены, процесс продолжит свое выполнение.

Секция on позволяет определить список сигналов, на изменение которых будет реагировать процесс. Когда выполнение процесса доходит до оператоpa wait, оно приостанавливается до момента, когда какой-либо из указанных в списке сигналов изменит значение.

Секция until позволяет определить булевское выражение, которое должно иметь значение true (для того, чтобы процесс продолжил выполнение после этой инструкции). Если же в момент выполнения оператора wait условие уже имело значение true, то выполнение процесса будет продолжено только после того, как заданное условие сначала примет значение false, а потом вновь значение true. Если команда содержит и секцию on, и секцию until, то булевское выражение, стоящее в until, проверяется только при условии, что произошло изменение какого-либо сигнала, стоящего в списке секции on.

|

|

|

Секция for позволяет определить интервал времени, на который процесс приостанавливается в модельном времени. Эта секция может задаваться вместе с двумя предыдущими. В таком случае процесс возобновит исполнение, как только условие, заданное одной из секций будет выполнено. Если присутствуют все три секции, то условие секции until проверяется только при изменении одного из сигналов, указанных в секции on.

Оператор wait может использоваться и без секций on, until, for. В этом случае выполнение wait приведет к остановке выполнения процесса до конца моделирования.

КОМПОНЕНТ. ДЕКЛАРАЦИЯ КОМПОНЕНТА НА ЯЗЫКЕ VHDL

Компонент — подсистема, объединенная сигналами.

Для того чтобы один объект моделирования мог быть включен в состав другого объекта, его необходимо декларировать как компонент — component.

Декларация компонента должна полностью совпадать с декларацией соответствующего ему объекта моделирования, но ключевое слово entity заменяется ключевым словом component.

Декларация компонента имеет следующий синтаксис:

component component_name is

[generic (generic_interface_list);]

|

|

|

[port (port_interface_list);]

end component [component_name] ;

Идентификатор component_name вводит имя компонента описываемого вида.

СТРУКТУРНОЕ ОПИСАНИЕ ОБЪЕКТА МОДЕЛИРОВАНИЯ НА ЯЗЫКЕ VHDL

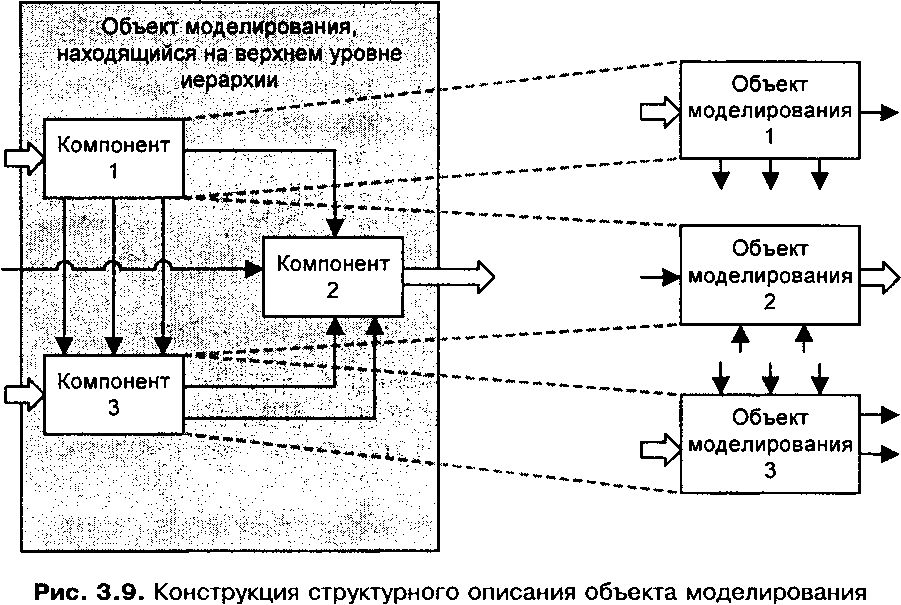

Структурное описание позволяет описать систему как совокупность компонентов — подсистем, объединенных сигналами. Подсистемы также являются объектами моделирования, но находятся на более низком уровне иерархии структурирования и представления проектируемого устройства. Каждая подсистема, в свою очередь, может быть представлена совокупностью подсистем, и так далее, пока на каком-то уровне не будет задано поведенческое описание архитектуры компонента, или не будет использован предопределенный компонент.

|

|

Каждый компонент, используемый в структурном описании, должен быть сам описан как объект моделирования (entity). Каждое такое описание может быть размещено в отдельном файле или библиотеке.

63. ОПИСАНИЕ ПЕРЕМЕННЫХ И КОНСТАНТ НА ЯЗЫКЕ VHDL . ЛИТЕРАЛЫ

Описание констант и переменных имеет сходную структуру. В начале строки описания указывается ключевое слово, определяющее вид описываемого объекта, затем указывается одно или несколько имен описываемых объектов и их тип. Для констант должно быть указано значение, для переменных указание начального значения возможно, но не обязательно.

|

|

|

Описание константы имеет следующий синтаксис:

constant name {,...}:subtype_indication := expression

Например:

constant address_length: integer:=4;

Описание переменной имеет следующий вид:

variable name{,...}: subtype_indication[:=eapression];

Например:

variable counter: integer:=7;

Литералом задается лексический элемент, который при компиляции кодируется некоторым числовым кодом.

Дата добавления: 2020-04-08; просмотров: 258; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!