Характеристика внутримашинного системного интерфейса

Лабораторная работа №1

Тема: Работа и особенности логических элементов

Цель работы: Познакомиться с основными базовыми логическими элементами

Литература:

1. Калабеков Б.А. Цифровые устройства и микропроцессорные системы. – М.: Горячая линия, 2005г

2. Калиш Г.Г. Основы вычислительной техники. – М. Высш. шк., 2000 г.

Краткие теоретические сведения:

| Логический элемент компьютера — это часть электронной логической схемы, которая реализует элементарную логическую функцию. |

Логическими элементами компьютеров являются электронные схемы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и другие (называемые также вентилями), а также триггер.

С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у вентилей бывает от двух до восьми входов и один или два выхода.

Чтобы представить два логических состояния — “1” и “0” в вентилях, соответствующие им входные и выходные сигналы имеют один из двух установленных уровней напряжения. Например, +5 вольт и 0 вольт.

Высокий уровень обычно соответствует значению “истина” (“1”), а низкий — значению “ложь” (“0”).

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Это упрощает запись и понимание сложных логических схем.

Работу логических элементов описывают с помощью таблиц истинности.

|

|

|

| Таблица истинности это табличное представление логической схемы (операции), в котором перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значением истинности выходного сигнала (результата операции) для каждого из этих сочетаний. |

Что такое схемы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ?

С х е м а И

Схема И реализует конъюнкцию двух или более логических значений.

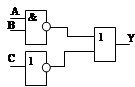

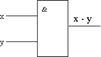

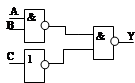

Условное обозначение на структурных схемах схемы И с двумя входами представлено на рис. 1. Таблица истинности — в таблице 1.

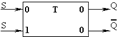

Рис. 1 Таблица 1

Рис. 1 Таблица 1

| x | y | X Y |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль.

Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x*y (читается как "x и y").

Операция конъюнкции на функциональных схемах обозначается знаком “&” (читается как "амперсэнд"), являющимся сокращенной записью английского слова and.

С х е м а ИЛИ

Схема ИЛИ реализует дизъюнкцию двух или более логических значений.

Когда хотя бы на одном входе схемы ИЛИ будет единица, на её выходе также будет единица.

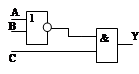

|

|

|

Знак “1” на схеме — от устаревшего обозначения дизъюнкции как ">=1" (т.е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1). Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x v y (читается как "x или y"). Таблица истинности — в табл. 2.

Таблица 2

| x | y | x v y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

С х е м а НЕ

Схема НЕ (инвертор) реализует операцию отрицания. Связь между входом x этой схемы и выходом z можно записать соотношением z =  , где

, где  читается как "не x" или "инверсия х".

читается как "не x" или "инверсия х".

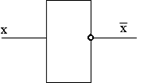

Если на входе схемы 0, то на выходе 1. Когда на входе 1, на выходе 0. Условное обозначение инвертора — на рисунке 3, а таблица истинности — в табл. 3.

Рис. 3 Таблица.3

Рис. 3 Таблица.3

| x |

|

| 0 | 1 |

| 1 | 0 |

С х е м а И - НЕ

Схема И-НЕ состоит из элемента И и инвертора и осуществляет отрицание результата схемы И.

Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  читается как "инверсия x и y".

читается как "инверсия x и y".

Таблица истинности схемы И-НЕ — в табл. 4.

Таблица 4

| x | y |

|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

С х е м а ИЛИ - НЕ

|

|

|

Схема ИЛИ-НЕ состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата схемы ИЛИ.

Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  , читается как "инверсия x или y". 0Таблица истинности схемы ИЛИ-НЕ — в табл. 5.

, читается как "инверсия x или y". 0Таблица истинности схемы ИЛИ-НЕ — в табл. 5.

Таблица 5

| x | y |

|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Триггер — это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю

Термин триггер происходит от английского слова trigger — защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает “хлопанье”. Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить (“перебрасываться”) из одного электрического состояния в другое и наоборот.

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс). Условное обозначение триггера — на рис.6.

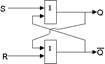

Рис.6

Рис.6

Он имеет два симметричных входа S и R и два симметричных выхода Q и  , причем выходной сигнал Q является логическим отрицанием сигнала

, причем выходной сигнал Q является логическим отрицанием сигнала  .

.

|

|

|

На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов (  ).

).

Наличие импульса на входе будем считать единицей, а его отсутствие — нулем.

На рис.7 показана реализация триггера с помощью вентилей ИЛИ-НЕ и соответствующая таблица истинности.

Рис.7

Рис.7

| S | R | Q |

|

| 0 | 0 | запрещено | |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | хранение бита | |

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ-НЕ (табл. 6).

- Если на входы триггера подать S=“1”, R=“0”, то (независимо от состояния) на выходе Q верхнего вентиля появится “0”. После этого на входах нижнего вентиля окажется R=“0”, Q=“0” и выход

станет равным “1”.

станет равным “1”. - Точно так же при подаче “0” на вход S и “1” на вход R на выходе

появится “0”, а на Q — “1”.

появится “0”, а на Q — “1”. - Если на входы R и S подана логическая “1”, то состояние Q и

не меняется.

не меняется. - Подача на оба входа R и S логического “0” может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 • 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

JK-триггер работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

Задание:

Вариант 1

Вариант 1

2. not (a and not B) or C

3. JK-триггер на элементах И-НЕ.

Вариант 2

Вариант 2

2. not (not A or B and not C)

3. RS-триггера на элементах И-НЕ.

Вариант 3

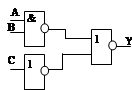

2. not ( А and not B) or C

3. D-триггер на элементах И-НЕ.

Вариант 4

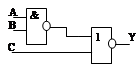

2. A or not (not B and C)

3. T-триггер на элементах И-НЕ.

Вариант 5

|

- not(not A or B or C)

- Двухтактный RS-триггера на элементах И-НЕ.

Порядок выполнения работы:

- По заданной логической схеме составить логическое выражение и заполнить для него таблицу истинности, нарисовать временную диаграмму входных и выходных сигналов.

- По заданному логическому выражению составить логическую схему и построить таблицу истинности, нарисовать временную диаграмму входных и выходных сигналов

- Нарисовать схему триггера, его условно-графическое обозначение. Построить таблицу истинности

Контрольные вопросы:

- Перечислите элементарные логические функции

- Назовите базовые логические элементы

- Что такое таблица истинности?

- Что такое регистр?

- Дайте определение понятию триггер?

- Какие виды триггеров вы знаете?

Отчет должен содержать:

- Логические схемы для каждого задания

- Логические выражения

- Ответы на контрольные вопросы.

Лабораторная работа №2

Тема: Работа логических узлов

Цель работы: Познакомиться с основными базовыми логическими узлами ЭВМ

Литература:

1. Калабеков Б.А. Цифровые устройства и микропроцессорные системы. – М.: Горячая линия, 2005г

- Калиш Г.Г. Основы вычислительной техники. – М. Высш. шк., 2000 г.

Краткие теоретические сведения:

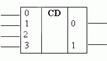

Дешифратором называется комбинационная схема, имеющая n входов и 2n выходов и преобразующая двоичный код на своих входах в унитарный код на выходах. Унитарным называется двоичный код, содержащий одну и только одну единицу, например 00100000. Условно-графическое обозначение дешифратора на три входа приведено на рис. 1.

Рис. 1. Условно-графическое обозначение трехвходового дешифратора

Номер разряда, в котором устанавливается "1" на выходе дешифратора, определяется кодом на его входах. Ниже приведена таблица истинности трехвходового дешифратора (таблица 1).

| Таблица 1. | |||||||||||

| Входы | Выходы | ||||||||||

| 2 | 1 | 0 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

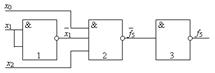

Реализация дешифратора в одноэлементном базисе "Штрих Шеффера" достаточно проста, так как таблица истинности для любого выхода имеет только одну единицу. На рис. 2 представлена схема формирования сигнала на одном из выходов дешифратора (сигнал f5 на выходе 5):

Рис. 2. Схема формирования сигнала на выходе 5 трехвходового дешифратора

Из представленной схемы видно, что фактически логику преобразования выполняет лишь элемент 2, в то время как элемент 1 служит для получения инверсии сигнала x1, а элемент 3 преобразует полученное на элементе 2 инверсное значение функции в прямое. Многие элементы хранения, например триггерные схемы, позволяют получать сигнал в парафазном коде, то есть имеют два выхода, на одном из которых сигнал имеет прямое, а на другом – инверсное значение. Это позволяет избавиться от элемента 1 в схеме. Если предположить, что значения выходных сигналов имеют инверсный вид по отношению к представленному в таблице 1, то отпадает необходимость в элементе 3. В большинстве реальных интегральных микросхем реализованы именно дешифраторы с инверсными выходами. Обозначение такого дешифратора показано на рис. 3.

Рис. 3. Условно-графическое обозначение дешифратора с инверсными выходами

На выходах такого дешифратора образуется унитарный код, содержащий один и только один ноль. Например, если входные сигналы имеют значение 1102=610, то выходы дешифратора, представленного на рис.3, будут находиться в состоянии 10111111, то есть выход 6 будет иметь значение, отличное от остальных выходов.

Дешифраторы широко применяются в различных устройствах компьютеров. Прежде всего, они используются для выбора ячейки запоминающего устройства, к которой производится обращение для записи или считывания информации. При этом часть разрядов адресного кода может дешифрироваться дешифраторами, выполненными в виде отдельных интегральных схем, а другая часть разрядов (обычно младшая) дешифрируется с помощью дешифраторов, встроенных непосредственно в БИС запоминающего устройства. Кроме того, дешифраторы находят применение в устройстве управления для определения выполняемой операции, построения распределителей импульсов и в других блоках.

Шифратор – схема, имеющая 2n входов и n выходов, функции которой во многом противоположны функции дешифратора (рис.4). Эта комбинационная схема в соответствии с унитарным кодом на своих входах формирует позиционный код на выходе (таблица 2).

Рис. 4. Условно-графическое обозначение шифратора на 4 входа

| Таблица 2. | |||||

| Входы | Выходы | ||||

| 3 | 2 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | х | 0 | 1 |

| 0 | 1 | Х | х | 1 | 0 |

| 1 | х | Х | х | 1 | 1 |

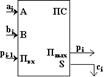

Сумматор — это электронная логическая схема, выполняющая суммирование двоичных чисел

Сумматор служит, прежде всего, центральным узлом арифметико-логического устройства компьютера, однако он находит применение также и в других устройствах машины.

Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров. Условное обозначение одноразрядного сумматора на рис. 5

Рис. 5

При сложении чисел A и B в одном i-ом разряде приходится иметь дело с тремя цифрами:

1. цифра ai первого слагаемого;

2. цифра bi второго слагаемого;

3. перенос pi–1 из младшего разряда.

В результате сложения получаются две цифры:

1. цифра ci для суммы;

2. перенос pi из данного разряда в старший.

Таким образом, одноразрядный двоичный сумматор есть устройство с тремя входами и двумя выходами, работа которого может быть описана следующей таблицей истинности:

| Входы | Выходы | |||

| Первое слагаемое | Второе слагаемое | Перенос | Сумма | Перенос |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

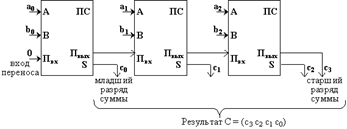

Если требуется складывать двоичные слова длиной два и более бит, то можно использовать последовательное соединение таких сумматоров, причём для двух соседних сумматоров выход переноса одного сумматора является входом для другого.

Например, схема вычисления суммы C = (с3 c2 c1 c0) двух двоичных трехразрядных чисел A = (a2 a1 a0) и B = (b2 b1 b0) может иметь вид:

Задание:

Вариант 1

1. 8-разрядный сумматор

2. дешифратор на 2 входа

Вариант 2

1. дешифратор на 4 входа

2. шифратор на 3 выхода

Вариант 3

1. шифратор на 4 выхода

2. 4-разрядный сумматор

Вариант 4

1. 5-разрядный сумматор

2. дешифратор на 3 входа

Вариант 5

- дешифратор на 5 входов

- шифратор на 2 выхода.

Порядок выполнения работы:

- Составить таблицы истинности

- Построить функциональные схемы

- Нарисовать временные диаграммы работы

Контрольные вопросы:

- Назначение дешифраторов

- Где применяются сумматоры

- Поясните организацию «запасного разряда»

Отчет должен содержать:

- Логические схемы для каждого задания

- Таблицы истинности

- Ответы на контрольные вопросы.

Лабораторная работа №3

Тема: CMOS. Конфигурация компьютера

Цель работы: Закрепить навыки работы с CMOS-памятью

Средства: ПК, Турбо СИ

Литература:

- Фролов А. В., Фролов Г.В. Аппаратное обеспечение IBM PC: В 2-х ч. – М.: «Диалог-Мифи»,1992г

- Айден К., Колесниченко О. Аппаратные средства PC. 2-е издание. – СПб.: BHV-Санкт-Петербург, 1998

Краткие теоретические сведения:

CMOS – память представляет собой энергонезависимую память, содержимое которой сохраняется после выключения компьютера. В CMOS - памяти хранится текущее время и дата, сведения о конфигурации системы, результат тестирования при включении питания и другая информация, приведенная в следующей таблице:

Рассмотрим подробно назначение отдельных ячеек CMOS-памяти.

00h - 0Dh - область часов реального времени

Ячейки с адресами 00h - 0Dh используются часами реального времени. Часам реального времени будет посвящена отдельная глава, поэтому сейчас мы не станем останавливаться на этих ячейках.

0Eh - байт состояния диагностики

Байт состояния диагностики (расположенный в CMOS - памяти по адресу 0Eh) содержит результаты выполнения диагностики при включении питания компьютера. Выполнив анализ содержимого байта 0Eh, программа может выявить неисправность НМД, часов реального времени, разрядку аккумулятора и ошибки в конфигурации. Приведем формат этого байта:

| Бит | Значение |

| 0 -1 | 1 Не используется, равно 0; |

| 2 | 0 - неправильная установка часов реального времени; 1 - часы реального времени установлены правильно; |

| 3 | 1 - неисправность НМД, невозможно загрузить операционную систему с жесткого диска; 0 - НМД исправен; |

| 4 | 1 - фактический размер оперативной памяти не соответствует указанному в CMOS-памяти; 0 - размер оперативной памяти указан правильно; |

| 5 | 1 - ошибка в конфигурации системы, фактическая конфигурация не соответствует указанной в байте конфигурации оборудования (адрес 14h); 0 - конфигурация указана правильно; |

| 6 | 1 - ошибка в контрольной сумме CMOS - памяти; 0 - контрольная сумма CMOS - памяти правильная; |

| 7 | 1 - разрядка аккумулятора, питающего CMOS - память и часы реального времени; 0 - аккумулятор исправен и заряжен |

0Fh - байт состояния отключения

Байт состояния отключения 0Fh используется процессорами 80286, 80386 и 80486 для определения способа возврата из защищенного режима в реальный после аппаратного сброса.

Эти процессоры могут работать либо в реальном режиме, который соответствует режиму работы процессора 8086, либо в защищенном. Защищенный режим работы используется такими операционными системами, как OS/2, UNIX, XENIX, а также операционными оболочками WINDOWS/386 и WINDOWS версии 3.0. В этом режиме процессор может непосредственно адресовать всю память, лежащую выше границы 1 мегабайт.

Перед выдачей команды отключения программа должна записать в ячейку 0Fh СMOS-памяти причину отключения:

| Значение | Причина отключения |

| 0 | Программный сброс при нажатии комбинации клавиш CTRL-ALT-DEL или неожиданный сброс. Выполняется обычный перезапуск системы, но процедуры тестирования при включении питания не выполняются. |

| 1 | Сброс после определения объема памяти |

| 2 | Сброс после тестирования памяти |

| 3 | Сброс после обнаружения ошибки в памяти (контроль четности). |

| 4 | Сброс с запросом перезагрузки |

| 5 | После сброса перезапускается контроллер прерываний, затем управление передается по адресу, который находится в области данных BIOS 0000:0467h |

| 6,7,8 | Сброс после выполнения теста работы процессора в защищенном режиме. |

| 9 | Сброс после выполнения пересылки блока памяти из основной памяти в расширенную |

| 0Аh | После сброса управление немедленно передается по адресу, взятому из области данных BIOS 0000:0467h |

Ссведения о команде отключения можно использовать для организации программного перезапуска системы.

10h - тип используемых флоппи-дисков;

Младшая и старшая тетрады этого байта описывают соответственно второй и первый НГМД:

0000 - дисковод не установлен;

0001 - дисковод на 360К;

0010 - дисковод на 1,2М;

0011 - дисковод на 720К;

0100 - дисковод на 1.44М.

11h - зарезервировано для AT, тип НМД для PS/2

В компьютерах PS/2 ячейки CMOS-памяти с адресами 11h и 12h используются для хранения типов, соответственно, первого и второго НМД.

12h - типы первого и второго НМД

Этот байт разделен на две тетрады аналогично байту, описывающему НГМД. Однако в тетраде можно закодировать только 16 различных значений, а типов НМД значительно больше. Поэтому тип 15 используется специальным образом - если тип НМД в младшей тетраде (диск C:) равен 15, то правильное значение типа находится в CMOS-памяти по адресу 19h. Аналогично для диска D: этот тип можно взять из байта по адресу 1Ah (если старшая тетрада байта с адресом 12h равна 15).

Таблица используемых типов дисков была приведена в третьей книге первого тома, в разделе, посвященном конфигурации дисковой подсистемы. Кроме того, сведения о типах дисков, задаваемых программой SETUP, обычно приводятся в документации, поставляемой вместе с компьютером.

13h - зарезервировано

Эта ячейка CMOS-памяти зарезервирована для дальнейшего развития системы.

14h - конфигурация оборудования

В этом байте находится информация о количестве установленных НГМД, о наличии арифметического сопроцессора 80287 или 80387 и о типе используемого дисплейного контроллера. Приведем формат байта конфигурации:

| Бит | Значение |

| 0 | 1 - в системе установлены НГМД; 0 - НГМД не используются |

| 1 | 1 - установлен арифметический сопроцессор 80287 или 80387; 0 - арифметический сопроцессор не установлен |

| 2-3 | не используются, равны 0 |

| 4-5 | тип дисплейного контроллера и его режим: Биты: 5 4 0 0 - не используется или EGA; 0 1 - CGA, EGA, VGA в режиме 40x25; 1 0 - CGA, EGA, VGA в режиме 80x25; 1 1 - монохромный контроллер |

| 6-7 | количество используемых НГМД: Биты: 7 6 0 0 - установлен 1 НГМД 0 1 - установлен 2 НГМД 1 0 - установлен 3 НГМД 1 1 - установлен 4 НГМД |

15h-16h - объем основной памяти

Ячейка 15h содержит младший байт, а ячейка 16h - старший байт объема основной памяти. Например:

0100h - 256K

0200h - 512K

0280h - 640K

17h-18h - объем дополнительной памяти

Ячейки 17h и 18h содержат, соответственно, младший и старший байты размера дополнительной памяти (расположенной выше границы 1 М) в килобайтах.

19h-1Ah типы первого и второго НМД

Эти ячейки содержат типы, соответственно, первого и второго НМД, если соответствующий тип имеет значение, большее 15 (см. описание ячейки 12h).

1Bh-2Dh - зарезервировано

Эти ячейки CMOS-памяти зарезервированы для дальнейшего развития системы.

2Eh-2Fh - контрольная сумма ячеек 10h - 20h

Для ячеек CMOS-памяти с адресами от 10h до 20h при инициализации системы BIOS выполняет проверку контрольной суммы. Эта контрольная сумма хранится также в CMOS-памяти в ячейках 2Eh и 2Fh (соответственно, старший и младший байты).

30h-31h - объем дополнительной памяти

Ячейки 30h и 31h содержат, соответственно, младший и старший байты размера дополнительной памяти (расположенной выше границы 1 М) в килобайтах.

Эта информация дублирует аналогичную информацию, расположенную в ячейках с адресами 17h-18h.

32h Текущее столетие

В машинах IBM AT этот байт содержит текущее столетие в двоично-десятичном коде, т.е. 19 столетие записано как 19h.

PS/2 использует эту ячейку вместе с ячейкой 33h для хранения контрольной суммы ячеек с адресами от 10h до 31h. При этом старший байт контрольной суммы хранится в ячейке 32h, а младший - 33h.

33h - различная информация

Для IBM AT этот байт используется программой SETUP.

34h-3Fh - зарезервировано

Это поле вы можете использовать по своему усмотрению, например, хранить здесь пароль.

PS/2 использует ячейку с адресом 37h для хранения номера текущего столетия. Ячейки 38h-3Fh в модели 50 компьютера PS/2 используются для хранения пароля. Обращение к этим ячейкам выполняется по адресам 78h-7Fh, которые аппаратно отображаются на адреса 38h-3Fh.

Задание:

Составить программу вывода содержимого ячеек CMOS-памяти в соответствии со своим вариантом и объяснить значение этой информации

| № варианта | Адрес | Значение |

| 1 | 0Eh | Байт состояния диагностики при включении питания |

| 2 | 0Fh | Байт состояния отключения |

| 3 | 10h | Тип используемого НГМД |

| 4 | 14h | Конфигурация оборудования |

| 5 | 15h - 16h | Объем основной памяти |

| 6 | 17h - 18h | Объем расширенной (extended) памяти |

| 7 | 30h - 31h | Объем расширенной (extended) памяти |

| 8 | 32h | Текущее столетие в двоично-десятичном коде (19h для 19-го столетия) |

Порядок выполнения работы:

- На основе разработанной программы в практической работе №4, создать программу вывода содержимого ячеек.

- Отладить программу

- Ответить на контрольные вопросы

Контрольные вопросы:

- Что из себя представляет CMOS-память?

- По какому адресу хранится информация об объеме ОЗУ?

- С какой целью используется байт состояния отключения?

Отчет должен содержать:

- Ответы на контрольные вопросы

Лабораторная работа №4

Тема: Интерфейсы

Цель работы: Познакомиться с основными видами интерфейсов ПК

Средства: ПК, шины SCSI, IDE, параллельный и последовательные порты и др.

Литература:

- Фролов А. В., Фролов Г.В. Аппаратное обеспечение IBM PC: В 2-х ч. – М.: «Диалог-Мифи»,1992г

- Айден К., Колесниченко О. Аппаратные средства PC. 2-е издание. – СПб.: BHV-Санкт-Петербург, 1998

Краткие теоретические сведения:

Характеристика внутримашинного системного интерфейса

Внутримашинный системный интерфейс - система связи и сопряжения узлов и блоков ЭВМ между собой - представляет собой совокупность электрических линий связи (проводов), схем сопряжения с компонентами компьютера, протоколов (алгоритмов) передачи и преобразования сигналов.

Существуют два варианта организации внутримашинного интерфейса.

1. Многосвязный интерфейс: каждый блок ПК связан с прочими блоками своими локальными проводами; многосвязный интерфейс применяется, как правило, только в простейших бытовых ПК.

2. Односвязный интерфейс: все блоки ПК связаны друг с другом через общую или системную шину.

В подавляющем большинстве современных ПК в качестве системного интерфейса используется системная шина. Структура и состав системной шины были рассмотрены ранее. Важнейшими функциональными характеристиками системной шины являются: количество обслуживаемых ею устройств и ее пропускная способность, т.е. максимально возможная скорость передачи информации. Пропускная способность шинызависит от ее разрядности (есть шины 8-, 16-, 32- и 64-разрядные) и тактовой частоты, на которой шина работает.

В качестве системной шины в разных ПК использовались и могут использоваться:

- шины расширений - шины общего назначения, позволяющие подключать большое число самых разнообразных устройств,

- локальные шины, специализирующиеся на обслуживании небольшого количества устройств определенного класса.

Сравнительные технические характеристики некоторых шин приведены в табл. 1.

Шины расширений

- Шина Multibus1 имеет две модификации: PC/XT bus (Persona) Computer eXtended Technology - ПК с расширенной технологией) и PC/AT bus (PC Advanced Technology - ПК с усовершенствованной технологией).

- Шина PC/XT bus - 8-разрядная шина данных и 20-разрядная шина адреса, рассчитанная на тактовую частоту 4,77 МГц; имеет 4 линии для аппаратных прерываний и 4 канала для прямого доступа в память (каналы DMA - Direct Memory Access). Шина адреса ограничивала адресное пространство микропроцессора величиной 1 Мбайт. Используется с МП 8086,8088.

- Шина PC/AT bus -16-разрядная шина данных и 24-разрядная шина адреса, рабочая тактовая частота до 8 МГц, но может использоваться и МП с тактовой частотой 16 МГц, так как контроллер шины может делить частоту пополам; имеет 7 линий для аппаратных прерываний и 4 канала DMA. Используется с МП 80286.

- Шине ISA (Industry Standard Architecture - архитектура промышленного стандарта) - 16-разрядная шина данных и 24-разрядная шина адреса, рабочая тактовая частота 8 МГц, но может использоваться и МП с тактовой частотой 50 МГц (коэффициент деления увеличен); по сравнению с шинами PC/XT и PC/AT увеличено количество линий аппаратных прерываний с 7 до 15 и каналов прямого доступа к памяти DMA с 7 до 11. Благодаря 24-разрядной шине адреса адресное пространство увеличилось с 1 до 16 Мбайт. Теоретическая пропускная способность шины данных равна 16 Мбайт/с, но реально она ниже, около 4-5 Мбайт/с, ввиду ряда особенностей ее использования. С появлением 32-разрядных высокоскоростных МП шина ISA стала существенным препятствием увеличения быстродействия ПК.

- Шина EISA (Extended ISA) - 32-разрядная шина данных и 32-разрядная шина адреса, создана в 1989 г. Адресное пространство шины 4 Гбайта, пропускная способность 33 Мбайт/с, причем скорость обмена по каналу МП - КЭШ - ОП определяется параметрами микросхем памяти, увеличено число разъемов расширений (теоретически может подключаться до 15 устройств, практически - до 10). Улучшена система прерываний, шина EISA обеспечивает автоматическое конфигурирование системы и управление DMA; полностью совместима с шиной ISA (есть разъем для подключения ISA), шина поддерживает многопроцессорную архитектуру вычислительных систем. Шина EISA весьма дорогая и применяется в скоростных ПК. сетевых серверах и рабочих станциях.

- Шина МСА (Micro Channel Architecture) -32-разрядная шина, созданная фирмой IBM в 1987 г. для машин PS/2, пропускная способность 76 Мбайт/с, рабочая частота 10-20 МГц. По своим прочим характеристикам близка к шине EISA, но не совместима ни с ISA, ни с EISA. Поскольку ЭВМ PS/2 не получили широкого распространения, в первую очередь ввиду отсутствия наработанного обилия прикладных программ, шина МСА также используется не очень широко.

Локальные шины

Современные вычислительные системы характеризуются:

- стремительным ростом быстродействия микропроцессоров (например, МП Pentium может выдавать данные со скоростью 528 Мбайт/с по 64-разрядной шине данных) и некоторых внешних устройств (так, для отображения цифрового полноэкранного видео с высоким качеством необходима пропускная способность 22 Мбайт/с);

- появлением программ, требующих выполнения большого количества интерфейсных операций (например, программы обработки графики в Windows, работа в среде Multimedia).

В этих условиях пропускной способности шин расширения, обслуживающих одновременно несколько устройств, оказалось недостаточно для комфортной работы пользователей, ибо компьютеры стали подолгу "задумываться".

Разработчики интерфейсов пошли по пути создания локальных шин, подключаемых непосредственно к шине МП, работающих на тактовой частоте МП (но не на внутренней рабочей его частоте) и обеспечивающих связь с некоторыми скоростными внешними по отношению к МП устройствами: основной и внешней памятью, видеосистемами и др,

Сейчас существуют два основных стандарта универсальных локальных шин: VLB и PCI

Шина VLB (VESA Local Bus -локальная шина VESA) - разработана в 1992 г. Ассоциацией стандартов видеооборудования (VESA - Video Electronics Standards Association), поэтому часто ее называют шиной VESA.

Шина VLB, no существу, является расширением внутренней шины МП для связи с видеоадаптером и реже с винчестером, платами Multimedia, сетевым адаптером. Разрядность шины - 32 бита, на подходе 64-разрядный вариант шины. Реальная скорость передачи данных по VLB - 80 Мбайт/с (теоретически достижимая -132 Мбайт/с).

Недостатки шины:

- рассчитана на работу с МП 80386, 80486, пока не адаптирована для процессоров Pentium, Pentium Pro, Power PC;

- жесткая зависимость от тактовой частоты МП (каждая шина VLB рассчитана только на конкретную частоту);

- малое количество подключаемых устройств - к шине VLB могут подключаться только четыре устройства;

- отсутствует арбитраж шины - могут быть конфликты между подключаемыми устройствами.

- Шина PCI (Peripheral Component Interconnect - соединение внешних устройств) - разработана в 1993 г. фирмой Intel.

Шина PCI является намного более универсальной, чем VLB, имеет свой адаптер, позволяющий ей настраиваться на работу с любым МП: 80486, Pentium, Pentium Pro, Power PC и др.; она позволяет подключать 10 устройств самой разной конфигурации с возможностью автоконфигурирования, имеет свой "арбитраж", средства управления передачей данных, Шина PCI пока еще весьма дорогая.

Разрядность PCI - 32 бита с возможностью расширения до 64 бит, теоретическая пропускная способность 132 Мбайт/с, а в 64-битовом варианте -263 Мбайт/с (реальная вдвое ниже).

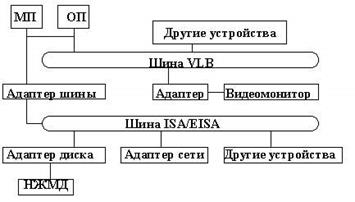

Шина РСI хотя и является локальной, выполняет и многие функции шины расширения, в частности, шины расширения ISA, EISA, MCA (а она совместима с ними) при наличии шины PCI подключаются не непосредственно к МП (как это имеет место при использовании шины VLB), а к самой шине PCI (через интерфейс расширения).

Варианты конфигурации систем с шинами VLB и PCI показаны соответственно на рис. 1 и 2 Следует иметь в виду, что использование в ПК шин VLB и PCI возможно только при наличии соответствующей VLB- или PCI-материнской платы. Выпускаются материнские платы с мультишинной структурой, позволяющей использовать ISA/EISA, VLB и PCI, так называемые материнские платы с шиной VIP (по начальным буквам VLB, ISA и PCI).

Рис. 1. Конфигурация системы с шиной VLB

Рис. 2. Конфигурация системы с шиной PCI

Таблица 1. Основные характеристики шин.

| Параметр | ISA | EISA | MCA | VLB | PCI |

| Разрядность шины, бит Данных Адреса | 16 24 | 32 32 | 32;64 32 | 32;64 32 | 32; 64 32 |

| Рабочая частота, МГц | 8 | 8-33 | 10-20 | до 33 | до 33 |

| Пропускная способность, Мбайт/с теоретическая практическая | 4 2 | 33 8 | 76 20 | 132 80 | 132;264 50;100 |

| Число подключаемых устройств, шт. | 6 | 15 | 15 | 4 | 10 |

Локальные шины IDE (Integrated Device Electronics), EIDE (Enhanced IDE), SCSI (Small Computer System Interface) используются чаще всего в качестве интерфейса только для внешних запоминающих устройств.

Задание:

Из представленных шин определить вид каждой, записать основные характеристики.

Порядок выполнения работы:

- Определить вид каждой шины

- Зарисовать ее разъём

- Определить как и к каким устройствам она подключается

- Ответить на контрольные вопросы

Контрольные вопросы:

- Что такое внутренний интерфейс ПК?

- Перечислите основные внутренние интерфейсы ПК.

- Назначение последовательного порта ПК

Отчет должен содержать:

- Наименования шин;

- Внешний вид разъемов;

- Ответы на контрольные вопросы

Практическая работа №1

Тема: Выполнение операций сложения и вычитания в обратном и дополнительном кодах

Цель работы: Научиться производить операции сложения и вычитания в дополнительных и обратных кодах

Литература:

1. Калабеков Б.А. Цифровые устройства и микропроцессорные системы. – М.: Горячая линия, 2005г

2. Калиш Г.Г. Основы вычислительной техники. – М. Высш. шк., 2000 г.

Краткие теоретические сведения:

Дата добавления: 2019-09-13; просмотров: 316; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!