Разработка функциональной схемы микроконтроллерной системы

Введение

Специальность «Компьютерные системы и сети» – одна из важнейших и наиболее универсальных в современной системе образования. В сферу ее интересов входят самые разнообразные объекты и устройства управления – от элементарных регуляторов до сложнейших систем управления производственными процессами и экспериментальными исследованиями.

Ввиду многоцелевого характера разработки и производства средств вычислительной техники важнейшее значение приобретает проблема дальнейшего повышения их эффективности, определяемой системой структурно-функциональных характеристик.

За последние годы в микроэлектронике бурное развитие получило направление, связанное с выпуском микроконтроллеров, которые предназначены для «интеллектуализации» оборудования различного назначения. Микроконтроллеры представляют собой приборы, конструктивно выполненные в виде БИС и включающие в себя все основные части «голой» микроЭВМ: микропроцессор, память программ и память данных, а также программируемые интерфейсные схемы для связи с внешней средой. Использование микроконтроллеров в системах управления обеспечивает достижения исключительно высоких показателей эффективности при столь низкой стоимости (во многих применениях система может состоять только из одной БИС микроконтроллера), что микроконтроллерам, видимо, нет разумной альтернативной элементной базы для построения управляющих и / или регулирующих систем.

К настоящему времени более двух третей мирового рынка микропроцессорных средств составляют именно микроконтроллеры.

Структурная организация, набор команд и аппаратурно-программные средства ввода-вывода информации микроконтроллеров лучше всего приспособлены для решения задач управления и регулирования в приборах устройствах и системах автоматики, а не для решения задач обработки данных.

Анализ технического задания

В данной курсовой работе необходимо спроектировать микропроцессорную систему на основе микроконтроллера К1816ВЕ31. Требуется описать и разработать структурную и функциональную схемы проектируемого устройства (системы), обосновать выбор конкретных элементов, разработать принципиальную схему проектируемого устройства (системы), разработать программу инициализации основных компонентов, а также программу функционирования на языке ассемблера микроконтроллера.

Разработка структурной схемы проектируемого устройства

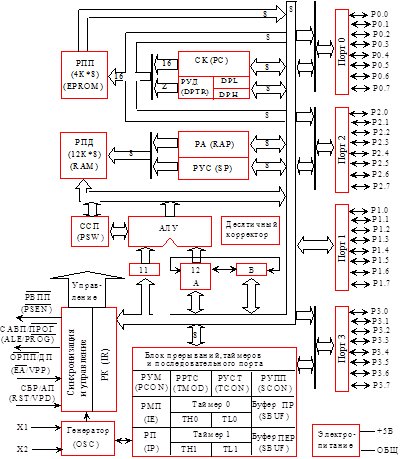

Основу структурной схемы микроконтроллера (рисунок 1) образует внутренняя двунаправленная 8-битная шина, которая связывает между собой все основные узлы и устройства: резидентную память, АЛУ, блок регистров специальных функций, устройство управления и порты ввода / вывода.

Арифметико-логическое устройство. 8-битное АЛУ может выполнять арифметические операции сложения, вычитания, умножения и деления; логические операции И, ИЛИ, исключающее ИЛИ, а также операции циклического сдвига, сброса, инвертирования и т.п. В АЛУ имеются программно недоступные регистры Т1 и Т2, предназначенные для временного хранения операндов, схема десятичной коррекции и схема формирования признаков.

Простейшая операция сложения используется в АЛУ для инкрементирования содержимого регистров, продвижения регистра-указателя данных и автоматического вычисления следующего адреса РПП. Простейшая операция вычитания используется в АЛУ для декрементирования регистров и сравнения переменных.

Простейшие операции автоматически образуют «тандемы» для выполнения в АЛУ таких операций, как, например, инкрементирование 16-битных регистровых пар. В АЛУ реализуется механизм каскадного выполнения простейших операций для реализации сложных команд. Так, например, при выполнении одной из команд условной передачи управления по результату сложения в АЛУ трижды инкрементируется СК, дважды производится чтение из РПД, выполняется арифметическое сравнение двух переменных, формируется 16-битный адрес перехода и принимается решение о том, делать или не делать переход по программе. Все перечисленные операции выполняются в АЛУ всего лишь за 2 мкс.

Важной особенностью АЛУ является его способность оперировать не только байтами, но и битами. Отдельные программно-доступные биты могут быть установлены, сброшены, инвертированы, переданы, проверены и использованы в логических операциях. Эта способность АЛУ оперировать битами столь важна, что во многих описаниях микропроцессора говорится о наличии в нем «булевского процессора». Для управления объектами часто применяются алгоритмы, содержащие операции над входными и выходными булевскими переменными (истина / ложь), реализация которых средствами обычных микропроцессоров сопряжена с определенными трудностями.

|

Рисунок -1. Структурная схема КР1816ВЕ31

АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется 51 различная операция пересылки или преобразования этих данных. Используется 11 режимов адресации (7 для данных и 4 для адресов), путем комбинирования «операция / режим адресации» базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции

Резидентная память. Память программ и память данных, размещенные на кристалле КР1816ВЕ31, физически и логически разделены, имеют различные механизмы адресации, работают под управлением различных сигналов и выполняют различные функции.

Память программ (ПЗУ или СППЗУ) имеет емкость 4Кбайта и предназначена для хранения команд, констант, управляющих слов инициализации, таблиц перекодировки входных и выходных переменных и т.п. РПП имеет 16-битную шину адреса, через которую обеспечивается доступ из счетчика команд или из регистра-указателя данных. Последний выполняет функции базового регистра при косвенных переходах по программе или используется в командах, оперирующих с таблицами.

Память данных (ОЗУ) предназначена для хранения переменных в процессе выполнения прикладной программы, адресуется одним байтом и имеет емкость 128 байт. Кроме того, к адресному пространству РПД примыкают адреса регистра специальных функций (РСФ), которые перечислены в таблице 3.

Память программ, также как и память данных, может быть расширена до 64Кбайт путем подключения внешних БИС.

Аккумулятор и ССП. Аккумулятор является источником операнда и местом фиксации результата при выполнении арифметических, логических операций и ряда операций передачи данных. Кроме того, только с использованием аккумулятора могут быть выполнены операции сдвига, проверка на нуль, формирование флага паритета и т.п.

Таблица 3.1

| Символ | Наименование | Адрес |

| * АСС | Аккумулятор | 0Е0Н |

| * В | Регистр-расширитель аккумулятора | 0F0Н |

| * PSW | Слово состояния программы | 0D0H |

| SP | Регистр-указатель стека | 81Н |

| DPTR | Регистр-указатель данных (DPH) (DPL) | 83H 82H |

| * P0 | Порт 0 | 80Н |

| * Р1 | Порт 1 | 90Н |

| * Р2 | Порт 2 | 0А0Н |

| * Р3 | Порт 3 | 0В0Н |

| * IP | Регистр приоритетов | 0В8Н |

| * IE | Регистр маски прерываний | 0А8Н |

| TMOD | Регистр режима таймера / счетчика | 89Н |

| * TCON | Регистр управления / статуса таймера | 88Н |

| TH0 | Таймер 0 (старший байт) | 8СН |

| TL0 | Таймер 0 (младший байт) | 8АН |

| TH1 | Таймер 1 (старший байт) | 8DН |

| TL1 | Таймер 1 (младший байт) | 8BН |

| Символ | Наименование | Адрес |

| * SCON | Регистр управления приемопередатчиком | 98Н |

| SBUF | Буфер приемопередатчика | 99Н |

| PCON | Регистр управления мощностью | 87Н |

Примечание. Регистры, имена которых отмечены знаком (*), допускают адресацию отдельных бит.

Таблица. 3.2

| Символ | Позиция | Имя и назначение |

| С | PSW.7 | Флаг переноса. Устанавливается и сбрасывается аппаратурными средствами или программой при выполнении арифметических и логических операциях |

| АС | PSW.6 | Флаг вспомогательного переноса. Устанавливается и сбрасывается только аппаратурными средствами при выполнении команд сложения и вычитания и сигнализирует о переносе или займе в бите 3. |

| F0 | PSW.5 | Флаг 0. Может быть установлен, сброшен или проверен программой как флаг, специфицируемый пользователем. |

| RS1 RS0 | PSW.4 PSW.3 | Выбор банка регистров. Устанавливается и сбрасывается программой для выбора рабочего банка регистров (см. примечание) |

| OV | PSW.2 | Флаг переполнения. Устанавливается и сбрасывается аппаратно при выполнении арифметических операций. |

| – | PSW.1 | Не используется. |

| Р | PSW.0 | Флаг паритета. Устанавливается и сбрасывается аппаратно в каждом цикле команды и фиксирует нечетное / четное число единичных бит в аккумуляторе, т.е. выполняет контроль по четности. |

Примечание. Выбор рабочего банка регистров

| RS1 | RS0 | Банк | Границы адресов |

| 0 | 0 | 0 | 00Н-07Н |

| 0 | 1 | 1 | 08Н-0FH |

| 1 | 0 | 2 | 10H-17H |

| 1 | 1 | 3 | 18H-1FH |

При выполнении многих команд в АЛУ формируется ряд признаков операции (флагов), которые фиксируются в регистре ССП. В таблице 4 приводится перечень флагов ССП, даются их символические имена и описываются условия их формирования.

Наиболее «активным» флагом ССП является флаг переноса, который принимает участие и модифицируется в процессе выполнения множества операций, включая сложение, вычитание и сдвиги. Кроме того, флаг переноса (С) выполняет функции «булевого аккумулятора» в командах, манипулирующих с битами. Флаг переполнения (OV) фиксирует арифметическое переполнение при операциях над целыми числами со знаком и делают возможным использование арифметики в дополнительных кодах. АЛУ не управляет флагами селекции банка регистров (RS0, RS1), и их значение полностью определяется прикладной программой и используется для выбора одного из четырех регистровых банков.

Структурная схема микроконтроллерной системы приведена в графической части курсового проекта приложение А

Разработка функциональной схемы микроконтроллерной системы

Разработка подсистемы памяти

В микроконтроллерных системах, построенных на основе КР1816ВЕ31, возможно использование двух типов внешней памяти: постоянной памяти программ (ВПП) и оперативной памяти данных (ВПД). Доступ к ВПП осуществляется при помощи управляющего сигнала RD, который выполняет функцию строб-сигнала, чтения. Доступ к ВПД обеспечивается управляющими сигналами RD и WR, которые формируются в линиях Р3.7 и Р3.6 при выполнении портом 3 альтернативных функций.

При обращении к ВПП всегда используется 16-битный адрес. Доступ к ВПД возможен с использованием 16-битного адреса (MOVX A,@DPTR) или 8-битного адреса (MOVX A,@RI).

В любых случаях использования 16-битного адреса старший байт адреса фиксируется (и сохраняется неизменным в течение одного цикла записи или чтения) в регистре-защелке порта 2.

Если очередной цикл внешней памяти (MOVX A,@DPTR) следует не сразу же за предыдущим циклом внешней памяти, то неизменяемое содержимое регистра-защелки порта 2 восстанавливается в следующем цикле. Если используется 8-битный адрес (MOVX A,@RI), то содержимое регистра-защелки порта 2 остается неизменным на его внешних выводах в течение всего цикла внешней памяти.

Через порт 0 в режиме временного мультиплексирования осуществляется выдача младшего байта адреса и передача байта данных. Сигнал САВП должен быть использован для записи байта адреса во внешний регистр. Затем в цикле записи выводимый байт данных появляется на внешних выводах порта 0 только перед появлением сигнала  . В цикле чтения вводимый байт данных принимается в порт 0 по фронту стробирующего сигнала

. В цикле чтения вводимый байт данных принимается в порт 0 по фронту стробирующего сигнала  .

.

При любом обращении к внешней памяти устройство управления КР1816ВЕ31 загружает в регистр защелку порта 0 код 0FFH, стирая тем самым информацию, которая могла в нем храниться.

Доступ к ВПП возможен при выполнении двух условий: либо на вход отключения резидентной памяти программ (  ) подается активный сигнал, либо содержимое счетчика команд превышает значение 0FFFH. Наличие сигнала

) подается активный сигнал, либо содержимое счетчика команд превышает значение 0FFFH. Наличие сигнала  необходимо для обеспечения доступа к младшим 4К адресам адресного пространства ВПП при использовании КР1816ВЕ31.

необходимо для обеспечения доступа к младшим 4К адресам адресного пространства ВПП при использовании КР1816ВЕ31.

Основная функция сигнала САВП – обеспечить временное согласование передачи из порта 0 на внешний регистр младшего байта адреса в цикле чтения из ВПП. Сигнал САВП приобретает значение 1 дважды в каждом машинном цикле. Это происходит даже тогда, когда в цикле выборки нет обращения к ВПП. Доступ к ВПД возможен только в том случае, если сигнал САВП отсутствует. Первый сигнал САВП во втором машинном цикле команды MOVX блокируется. Следовательно, в любой МК-системе, не использующей ВПД, сигнал САВП генерируется с постоянной частотой, равной 1/16 частоты резонатора, и может быть использован для синхронизации внешних устройств или для реализации различных временны функций.

При обращении к РПП сигнал  не генерируется, а при обращении к ВПП он выполняет функцию строб-сигнала чтения. Полный цикл чтения ВПД, включая установку и снятия сигнала

не генерируется, а при обращении к ВПП он выполняет функцию строб-сигнала чтения. Полный цикл чтения ВПД, включая установку и снятия сигнала  , занимает 12 периодов резонатора.

, занимает 12 периодов резонатора.

Особый режим работы КР1816ВЕ31. Содержимое памяти программ КР1816ВЕ31 заполняется единожды на этапе разработки МК-системы и не может быть модифицировано в завершенном изделии. По этой причине микроконтроллеры не являются машинами классической «фон-неймановской» архитектуры. Оперативная память данных не может быть использована для хранения кодов программы. Эта особенность архитектуры МК объясняется тем, что в большинстве применений МК требуется наличие одной неизменяемой прикладной программы, хранимой в ПЗУ, наличие ОЗУ небольшой емкости для временного хранения переменных и эффективных, а следовательно, разных методов адресации памяти программ и памяти данных.

Микроконтроллер КР1816ВЕ31 не имеет внутренней памяти программ и поэтому пользуется только внешней памятью, которую можно модифицировать путем перепрожига внешней микросхемы ПЗУ.

Тип микропроцессора К1816ВЕ31. Объем внешнего ОЗУ – 4Кбайт. В данном микропроцессоре (в соответствии со структурой команд) внешняя адресация памяти данных позволяет адресовать 64Кбай внешней памяти. Для разработки подсистемы памяти выбираем микросхему в соответствии с перечнем элементов, приведенных в приложении Г.

Дата добавления: 2019-07-15; просмотров: 362; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!