Разработка программного обеспечения

Федеральное агентство по образованию

Государственное образовательное учреждение

Высшего профессионального образования

«Тульский государственный университет»

Кафедра «Системы автоматического управления»

Курсовая работа

По дисциплине

ЭВМ И ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ

На тему

"РАЗРАБОТКА МПС"

Тула 2004 г.

Введение

Одним из крупнейших достижений микроэлектроники и вычислительной техники является создание микропроцессоров (микропроцессорных наборов БИС). В решении актуальных задач ускорения научно-технического прогресса им принадлежит существенная роль.

Высокая производительность, малые габаритные размеры и энергопотребление, эргономичность, развитое, ориентированное на массового пользователя базовое и прикладное программное обеспечение микроЭВМ и ПЭВМ обеспечивают значительное повышение эффективности труда в различных отраслях народного хозяйства. Это особенно важно при автоматизации сложной управленческой, хозяйственной, инженерной детельности, научных исследований и экспериментов, учебного процесса.

Массовый выпуск микропроцессорных наборов БИС с широкими функциональными возможностями, их низкая стоимость, гибкость и точность цифровых методов обработки информации превратили МП в системные элементы, на основе которых создаются системы промышленной автоматики, связи, измерительной техники, управления транспортом и т.д.

|

|

|

Создание МПС на базе МП содержит два этапа: разработка аппаратной части и разработка программного обеспечения на языке низкого уровня (языка кодовых комбинаций, Ассемблера).

В данной работе рассматривается пример разработки микропроцессорной системы, которая является ПИД-регулятором.

Выбор микропроцессора

Исходя из данных задания (разрядность, тактовая частота, общий объём памяти) выбираем процессор Z80 фирмы Zilog.

Схема подключения микропроцессора показана на рис. 1

Рисунок 1. Схема подключения микропроцессора

По заданию (вторая часть) на входе МПС – 16‑ти битный сигнал ошибки САУ  , синхронный со срезами внешнего синхросигнала постоянной частоты со скважностью

, синхронный со срезами внешнего синхросигнала постоянной частоты со скважностью  (меандр). Следовательно МПС должна начать обрабатывать новый сигнал, как только он поступил. Этот процесс организован с помощью подключения синхросигнала с выходу маскируемого прерывания

(меандр). Следовательно МПС должна начать обрабатывать новый сигнал, как только он поступил. Этот процесс организован с помощью подключения синхросигнала с выходу маскируемого прерывания  .

.

Организация памяти

Шестнадцатибитная линия адреса процессора Z80 при разрядности 8 бит позволяет адресовать 64 Кбайта памяти и 512 устройств ввода\вывода (256 ввода, 256 вывода).

По заданию требуется спроектировать блок памяти:

|

|

|

· ПЗУ – 32 Кслов (32Кбайт),

· ОЗУ – 8 Кслов (8Кбайт).

Для хранения 32 Кбайт ПЗУ используем четыре микросхемы 573РФ4 (объём 65536 бит, организация 8192×8)

Для хранения 8 Кбайт ОЗУ – четыре микросхемы 537РУ10 (объём 16384 бит, организация 2048×8).

Составим карту памяти (табл. 1), исходя из того, что ПЗУ занимает нижние адреса памяти, адреса ОЗУ следуют за ПЗУ, остальные 24 Кбайта не используются.

Таблица 1. Карта памяти

| Номер бита | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

| ПЗУ | Банк 1 (8 кб) | 0000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 1FFF | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| Банк 2 (8 кб) | 2000 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 3FFF | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| Банк 3 (8 кб) | 4000 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 5FFF | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| Банк 4 (8 кб) | 6000 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 7FFF | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| ОЗУ | Банк 1 (2 кб) | 8000 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 87FF | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| Банк 2

(2 кб) | 8800 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 8FFF | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| Банк 3 (2 кб) | 9000 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 97FF | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| Банк 4 (2 кб) | 9800 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 9FFF | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

Из табл. 1 можно сделать следующие выводы по организации памяти:

· Шина данных подключается сразу ко всем восьми микросхемам.

· Для выбора той или иной микросхемы достаточно одного двойного демультиплексора 531ИД14, осуществляющего преобразование 1ð4. Одна его часть отвечает за выбор схемы ПЗУ, другая – за выбор ОЗУ.

· Бит А15 равен 0, если адресуется ПЗУ и равен 1, когда адресуется ОЗУ.

· ПЗУ. По линии адреса на микросхему подаются биты А0‑А12, биты А13 и А14 определяют, в какой именно банк происходит адресация.

· ОЗУ. По линии адреса на микросхему подаются биты А0‑А10, биты А11 и А12 определяют конкретный банк, биты А13 и А14 всегда равны 0.

Сигналы с выхода демультиплексора подаются непосредственно на входы  в ПЗУ и на входы

в ПЗУ и на входы  в ОЗУ.

в ОЗУ.

Для активизации демультиплексора, отвечающего за ПЗУ, на вход  необходимо подавать активный уровень сигнала (логический 0), если происходит цикл обращения к памяти (

необходимо подавать активный уровень сигнала (логический 0), если происходит цикл обращения к памяти (  ) и

) и  . Необходимый управляющий сигнал достигается при использовании логического функции

. Необходимый управляющий сигнал достигается при использовании логического функции  и элемента дисъюнктора. Справедливы аналогичные рассуждения для демультиплексора, отвечающего за ОЗУ, за исключением того факта, что в дисъюнкцию должно войти отрицание элемента

и элемента дисъюнктора. Справедливы аналогичные рассуждения для демультиплексора, отвечающего за ОЗУ, за исключением того факта, что в дисъюнкцию должно войти отрицание элемента  –

–  .

.

|

|

|

На вход  ОЗУ необходимо подать логическую функцию

ОЗУ необходимо подать логическую функцию  (логическое

(логическое  , элемент конъюнктор), а на вход

, элемент конъюнктор), а на вход  – выход МП

– выход МП  .

.

Напряжения.

Т.к. ПЗУ не находится в режиме программирования, то на входы питания ПЗУ (  ,

,  ,

,  ) требуется подать +5V, а входы

) требуется подать +5V, а входы  и

и  – заземлить (на рис. не показано).

– заземлить (на рис. не показано).

На вход ОЗУ  также подаётся +5V, а вход

также подаётся +5V, а вход  заземляется.

заземляется.

Схема подключения памяти к шинам представлена на рис. 2.

Рисунок 2. Организация памяти

Организация ввода\вывода

По заданию МПС должна принимать и выдавать 16 ти битный код. Кроме того у МПС имеются перемычки для задания шестнадцатибитных констант регулятора  ,

,  ,

,  .

.

На МПС должны быть 48 (16×3) перемычек для задания констант. Схема организации перемычек представлена на рис. слева. Перемычки собираются в группы по восемь (например, младший байт константы

На МПС должны быть 48 (16×3) перемычек для задания констант. Схема организации перемычек представлена на рис. слева. Перемычки собираются в группы по восемь (например, младший байт константы  ) и подаются на приёмопередатчик 580ВА86. Таким образом задание трёх шестнадцатибитных констант требует шести 8‑ми битных приёмопередатчиков.

) и подаются на приёмопередатчик 580ВА86. Таким образом задание трёх шестнадцатибитных констант требует шести 8‑ми битных приёмопередатчиков.

Входной и выходной сигналы целесообразно хранить в регистрах, где они будут дожидаться запроса МП на чтение при вводе и запроса внешнего устройства (фронта синхросигнала) при выводе кода. Таким образом требуется наличие четырёх 8‑ми битных регистров.

Всего же требуется адресовать 10 устройств ввода\вывода. При этом задействуются биты А0‑А3. Запишем адреса внешних устройств в табл. 3.

Таблица 2. Адреса внешних устройств

| N | Внешний сигнал | Адрес |

| 1 | Входной сигнал | 0001:0000 |

| 2 |

| 0011:0010 |

| 3 |

| 0101:0100 |

| 4 |

| 0111:0110 |

| 5 | Выходной сигнал | 1001:1000 |

Обращение к тому или иному внешнему сигналу в зависимости от его адреса осуществим с помощью демультиплексора 555ИД7 1ð8 и дополнительных логических элементов. На вход демультиплексора подаются биты А0‑А2. Бит А3 отвечает за то, осуществляется ли адресация к портам ввода или вывода.

Рассмотрим случай адресации к младшему байту порта ввода данных или вывода. Обозначим  – сигнал с выхода демультиплексора №0,

– сигнал с выхода демультиплексора №0,  – сигнал, который подаётся на регистр, отвечающий за приём входного кода,

– сигнал, который подаётся на регистр, отвечающий за приём входного кода,  – сигнал, отвечающий за запись в регистр выходного кода. Составим таблицу истинности (табл. 2). При этом необходимо помнить, что у

– сигнал, отвечающий за запись в регистр выходного кода. Составим таблицу истинности (табл. 2). При этом необходимо помнить, что у  активный уровень

активный уровень  (подключается к входу

(подключается к входу  ), а

), а  – сигнал положительной логики (подключается к входу

– сигнал положительной логики (подключается к входу  ).

).

Таблица 3. Таблица истинности

|

|

|

|

| 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 |

Используя СКНФ, СДНФ и теорему де Моргана, запишем логические функции:

,

,  .

.

Очевидно, что демультиплексор активируется, когда происходит цикл обращения к внешним устройствам (  ) и хотя бы один из сигналов

) и хотя бы один из сигналов  или

или  равен нулю.

равен нулю.

.

.

Сокращённая схема подключения устройств ввода\вывода изображена на рис. 3.

Общий вид МПС достигается совмещением рис. 1–3 на одном и соединением магистралей (шины данных, адреса и управления).

Рисунок 3. Проектирование устройств ввода\вывода

Разработка программного обеспечения

В соответствии с заданием программа разрабатывается на Ассемблере с использованием системы команд выбранного процессора.

Логически программа состоит из двух частей:

· основная часть программы для задания констант;

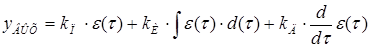

· программа обработки прерывания – получения входного шестнадцатибитного кода, выполнение математической операции и выдача шестнадцатибитного кода – результата математической операции:

. (1)

. (1)

Интеграл и дифференциал

Интеграл и дифференциал считаются по приближённым формулам:

·

·  .

.

В данных выражениях  – период внешнего синхросигнала. В расчётах этот множитель участвовать не будет, а результат будет выдаваться пропорционально его значению.

– период внешнего синхросигнала. В расчётах этот множитель участвовать не будет, а результат будет выдаваться пропорционально его значению.

Дата добавления: 2019-07-15; просмотров: 164; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!