ЗАДАНИЕ И ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

Московский государственный технический университет

имени Н. Э. Баумана

И.А. Васильев, Е.С. Люминарская, К.В. Селиванов

Исследование триггеров

Методические указания к выполнению лабораторной работы по курсу

«Электротехника и электроника»

Москва

(С) 201_ МГТУ им. Н.Э. БАУМАНА

УДК 621.3

ББК 31.2

Рецензент

кандидат технических наук, доцент

О.И. Мисеюк

| Васильев И.А., Люминарская Е.С., Селиванов К.В. | |

| Исследование триггеров: Методические указания к лабораторной работе по курсу «Электротехника и электроника» / И.А. Васильев, Е.С. Люминарская. — Москва : Издательство МГТУ им. Н.Э. Баумана, 2017. – 28 с.: ил. | |

| ISBN Изложены краткие теоретические сведения, необходимые для изучения основных схем асинхронных и синхронных триггеров. Дано описание лабораторной работы. Приведен порядок выполнения работы. Для студентов 3 и 4 курса факультетов МТ, ФН МГТУ им. Н.Э. Баумана, изучающих дисциплину «Электротехника и электроника». Рекомендовано учебно-методической комиссией НУК ФН МГТУ им. Н.Э. Баумана.

| |

© Васильев И.А., Люминарская Е.С.,Селиванов К.В. 2017

© МГТУ им. Н.Э. Баумана, 2017

Оглавление

Предисловие ……………………………………………………………………...4

1. Основные теоретические сведения…………………………………………...5

1.1. Асинхронный RS-триггер.………………………………………………6

|

|

|

1.2. Синхронный RS-триггер.……………………………...………………...9

1.3. Синхронный D-триггер...………..……………….…………………….11

1.4. Двухступенчатый RS-триггер...……………..…………………………12

1.5. Счетный Т-триггер……………………………………………………...12

1.6. Универсальный JK-триггер…………………………………………….13

2. Основы работы в программной среде MULTISIM ……………………...……..16

3. Задание и порядок выполнения работы……………………………………..20

3.1. Асинхронный RS-триггер на элементах ИЛИ-НЕ………..………….20

3.2. Асинхронный RS-триггер на элементах И-НЕ…………...…………..21

3.3. Синхронный RS-триггер……..................................................................22

3.4. Синхронный D-триггер…………………………………………………23

3.5. Двухступенчатый RS-триггер...………………………………..............24

3.6. Универсальный JK-триггер…………………………………………….25

Требования к отчету……………………………………………………………..27

Заключение……………………………………………………………………….28

Вопросы для самоконтроля……………………………………………………..28

Литература……………………………………………………………………….29

ПРЕДИСЛОВИЕ

Все цифровые электронные устройства (ЦЭУ) делятся на комбинационные и последовательностные. Состояние выходов комбинационного ЦЭУ в любой момент времени определяется только комбинацией логических сигналов на его информационных входах. Состояние выходов последовательностного ЦЭУ в каждый момент времени определяется не только комбинацией логических сигналов на входах, но и последовательностью их поступления в предыдущие моменты времени, т.е. появляется потребность в некоторого рода памяти, которая позволяет осуществлять последовательность операций. Роль такой «ячейки памяти» и выполняют триггеры.

|

|

|

Лабораторная работа «Исследование триггеров» предусмотрена учебным планом дисциплины «Электротехника и электроника» для студентов 4 курса факультетов МТ, ФН.

Цель лабораторной работы. Ознакомление с основными схемами триггеров, изучение принципа действия асинхронных и синхронных триггеров.

Задачи лабораторной работы. Экспериментально исследовать законы функционирования (режимы работы) асинхронного RS-триггера, синхронного RS-триггера, D-триггера, двухступенчатого RS-триггера и универсального JK-триггера в программном комплексе Multisim. Для каждого триггера составить таблицу переходов.

Приобретаемые умения – анализ и синтез логических схем, построение основных схем асинхронных и синхронных триггеров в программной среде Multisim.

|

|

|

Приобретаемые знания – функциональные возможности асинхронного и синхронного RS-триггерa, D-триггерa, счетного Т-триггера, двухступенчатого RS-триггера, универсального JK-триггера и различные способы хранения информации в них.

ОСНОВНЫЕ ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

Триггером называют устройство, которое может находиться в одном из двух устойчивых состояний и переходить из одного состояния в другое под воздействием активного уровня логических сигналов, поступающих на его информационные входы. Важно отметить, что после переключения триггера входной активный сигнал может быть снят, а триггер будет оставаться в том состоянии, которое он приобрел при воздействии этого сигнала. Таким образом, триггер является простейшим элементом памяти, способным хранить один бит информации.

Закон функционирования триггера часто задают таблицей истинности, которая отражает процесс перехода триггера из одного устойчивого состояния в другое, или временной диаграммой, показывающей уровни напряжения и временные интервалы между входными и выходными сигналами.

Триггеры имеют два выхода – прямой  и инверсный

и инверсный  . О состоянии триггера судят по сигналу на прямом выходе. Если триггер установлен, то на его прямом выходе будет логическая 1, а на инверсном – логический 0.

. О состоянии триггера судят по сигналу на прямом выходе. Если триггер установлен, то на его прямом выходе будет логическая 1, а на инверсном – логический 0.

|

|

|

Применительно к схемам триггеров различают следующие наименования (функциональные назначения) входов:

S – информационный, для раздельного перевода триггера в состояние 1;

R – информационный, для раздельного перевода триггера в состояние 0;

D – информационный, для установки триггера в состояние 1 или 0;

J – информационный, для установки универсального JK-триггера в состояние 1;

K – информационный, для установки универсального JK-триггера в состояние 0;

С – тактовый (синхронизирующий);

Т – счетный.

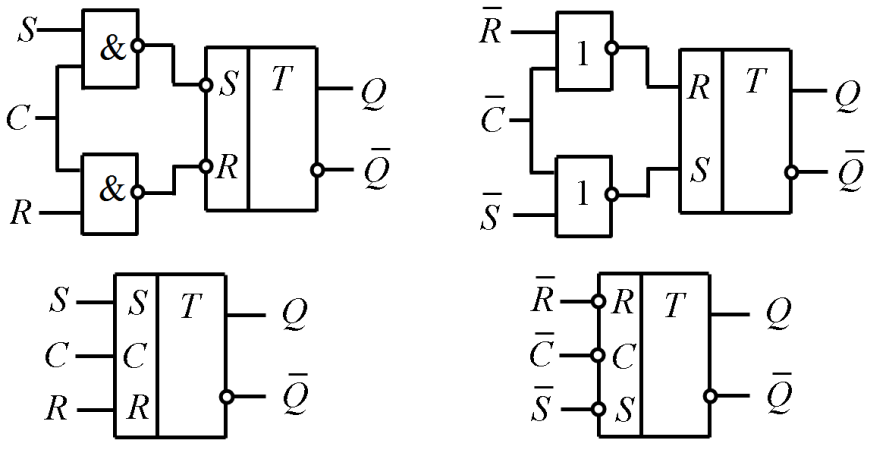

В триггерах различают прямые и инверсные входы. В прямых входах активным считают высокий уровень напряжения (логической 1), в инверсных входах – низкий уровень напряжения (логического 0). Условное обозначение прямых и инверсных входов показано на рис.1.

Рис. 1. Условное обозначение прямых а и инверсных б входов

По функциональным возможностям различают:

1) триггеры с раздельной установкой состояний 0 и 1(RS-триггеры);

2) триггеры со счетным входом (Т-триггеры);

3) триггеры задержки с приемом информации по одному входу (D-триггеры);

4) универсальные триггеры с информационными входами K и J (JK-триггеры).

По способу записи информации различают асинхронные и синхронные (тактируемые) триггеры. В асинхронных триггерах запись информации осуществляется одновременно с поступлением сигнала на информационные входы, в синхронных триггерах – при подаче синхроимпульса. Помимо этого, синхронные триггеры могут быть со статическим и динамическим управлением. Триггеры со статическим управлением воспринимают информационные сигналы при подаче на вход С логической 1 (прямой вход) или логического 0 (инверсный вход). Триггеры с динамическим управлением воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (фронт импульса) или от 1 к 0 (срез импульса). На рис.2 представлены варианты обозначения динамических входов на выводах цифровых микросхем.

а б

Рис. 2. Варианты обозначения динамических входов на выводах цифровых микросхем:

а – вход, срабатывающий по фронту импульса, б - вход, срабатывающий по срезу импульса

1.1. Асинхронный RS -триггер

Асинхронным RS-триггером называют запоминающий элемент с двумя разделенными информационными входами для установки его в состояние «1» (S-вход) или в состояние «0» (R-вход).

В общем виде таблица истинности RS-триггера представлена на рис.3. В приведенной таблице:  – значения логических переменных в момент времени t на соответствующих входах триггера;

– значения логических переменных в момент времени t на соответствующих входах триггера;  – значения логической переменной на выходе триггера в момент времени t (до переключения) и t+1(после переключения);

– значения логической переменной на выходе триггера в момент времени t (до переключения) и t+1(после переключения);  – неопределенные коэффициенты в тех наборах, где входные сигналы триггера образуют запрещенную комбинацию. Запрещенная комбинация входных сигналов – это одновременная подача активных уровней на все информационные входы. При R=S=1 состояние триггера будет неопределенным, так как во время действия данных информационных сигналов логические уровни на выходах триггера одинаковы, и после окончания их действия триггер может равновероятно принять одно из двух устойчивых состояний.

– неопределенные коэффициенты в тех наборах, где входные сигналы триггера образуют запрещенную комбинацию. Запрещенная комбинация входных сигналов – это одновременная подача активных уровней на все информационные входы. При R=S=1 состояние триггера будет неопределенным, так как во время действия данных информационных сигналов логические уровни на выходах триггера одинаковы, и после окончания их действия триггер может равновероятно принять одно из двух устойчивых состояний.

|

|

|

|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 |

|

| 1 | 1 | 1 |

|

Рис. 3.Обобщенная таблица истинности RS-триггера

Карта Карно, соответствующая данной таблице, приведена на рис.4, а. На рис.4, б и рис.4, в неопределенные коэффициенты  заменены на 1 и 0 соответственно.

заменены на 1 и 0 соответственно.

a б в

Рис. 4. Карта Карно для таблицы переходов RS-триггера:

а – карта Карно с неопределенными коэффициентами  б – карта Карно c коэффициентами

б – карта Карно c коэффициентами  ; в – карта Карно c коэффициентами

; в – карта Карно c коэффициентами

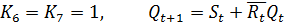

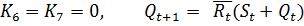

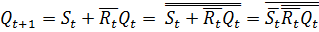

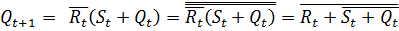

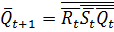

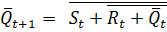

Из карт Карно получаем логические уравнения асинхронного RS-триггера:

при  ; (1)

; (1)

при  . (2)

. (2)

Воспользовавшись теоремой де Моргана, представим выражение (1) в базисе И-НЕ, а выражение (2) – в базисе ИЛИ-НЕ:

, (3)

, (3)  . (4)

. (4)

Аналогично можно получить выражения для инверсного выхода в базисе И-НЕ и в базисе ИЛИ-НЕ соответственно:

, (5)

, (5)

. (6)

. (6)

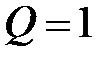

Формулы (3) и (5) позволяют получить структурную схему асинхронного RS-триггера с инверсными входами, построенного на базе логических элементов И-НЕ. Условное обозначение, схема, таблица истинности и временная диаграмма этого триггера представлены на рис. 5. Переключение триггера выполняется логическим «0», подаваемым на вход R (режим записи 0) или S (режим записи 1). Запрещенная комбинация соответствует логическим «0» на обоих входах. При подаче на входы логических «1» обеспечивается хранение информации.

Подключение каждого элемента к одному из выходов другого элемента обеспечивает триггеру два устойчивых состояния. Например, пусть на входы R и S подаются единичные потенциалы. Если на выходе верхнего логического элемента "И-НЕ" Q присутствует логический ноль, то на выходе нижнего логического элемента "И-НЕ" появится логическая единица. Эта единица подтвердит логический ноль на выходе Q.

На временной диаграмме (см. рис. 5, г) видно, что в момент времени  на вход S начинает подаваться сигнал

на вход S начинает подаваться сигнал  , а на входе R сигнал

, а на входе R сигнал  не изменяется. По таблице истинности можно определить, что в рассматриваемый момент времени сигнал на прямом выходе изменится с

не изменяется. По таблице истинности можно определить, что в рассматриваемый момент времени сигнал на прямом выходе изменится с  на

на  . Аналогично определяются изменения сигнала

. Аналогично определяются изменения сигнала  в моменты времени

в моменты времени  .

.

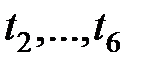

На рис. 6, а представлена структурная схема асинхронного RS-триггера с прямыми входами, построенного по формулам (4) и (6) на базе логических элементов ИЛИ-НЕ. Условное обозначение, таблица истинности и временная диаграмма приведены на рис. 6, б, в и г соответственно.

Следует отметить, что самостоятельно RS-триггеры в устройствах цифровой техники используют ограниченно из-за низкой помехоустойчивости.

Рис. 5. Асинхронный RS-триггер с инверсными входами на базе И-НЕ:

а – структурная схема; б – условное обозначение; в – таблица истинности; г – временная диаграмма

Рис. 6. Асинхронный RS-триггер с прямыми входами на базе И-НЕ:

а – структурная схема; б – условное обозначение; в – таблица истинности, г – временная диаграмма

Синхронный RS-триггер

Для построения синхронного RS-триггера можно взять за основу структурную схему асинхронного триггера и дополнить ее так называемой блокирующей ячейкой. Эта ячейка не допускает информационные сигналы R и S на входы асинхронного RS-триггера, пока на С-входе отсутствует сигнал синхронизации.

Таким образом, при активном уровне сигнала на С-входе (C =1) асинхронный RS-триггер в составе синхронного триггера работает обычным образом, а при пассивном (C=0) – находится в режиме хранения предыдущего состояния.

Схемы и условные обозначения синхронных RS-триггеров приведены на рис.7. На рис.7, а представлен синхронный RS-триггер, построенный на базе логических элементов И-НЕ, а на рис.7, б – синхронный RS-триггер, построенный на базе логических элементов ИЛИ-НЕ.

a б

Рис. 7. Схемы и условные обозначения синхронных RS-триггеров:

а – синхронный RS-триггер в базисе И-НЕ, б – синхронный RS-триггер в базисе ИЛИ-НЕ

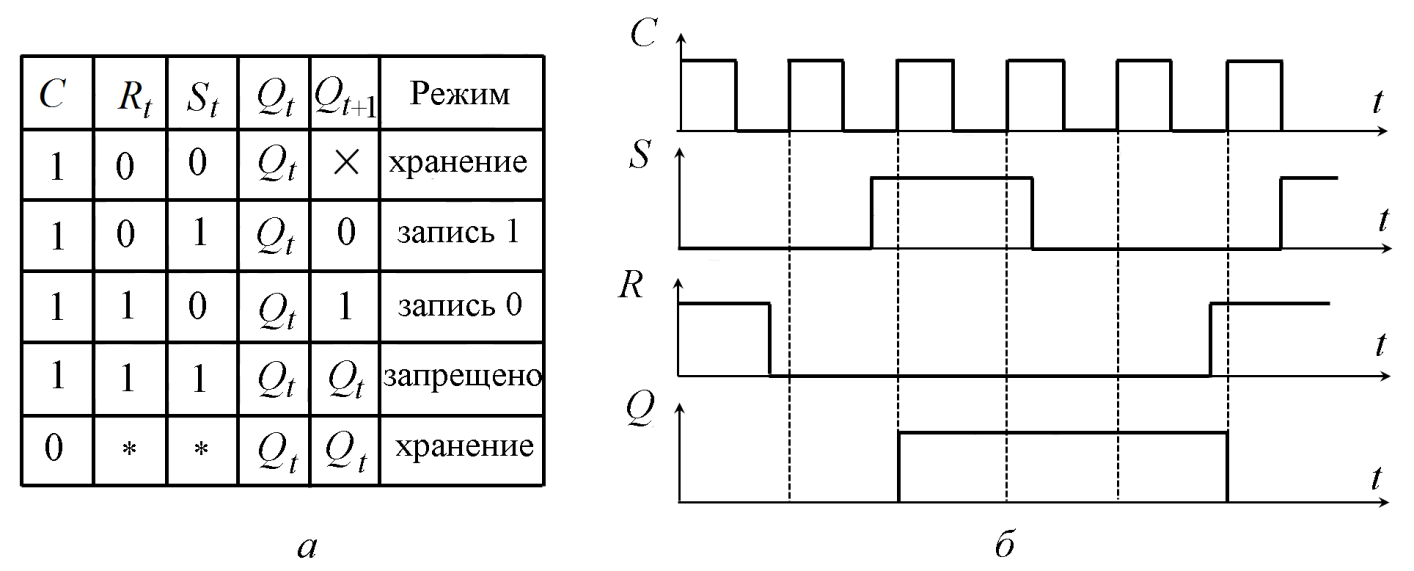

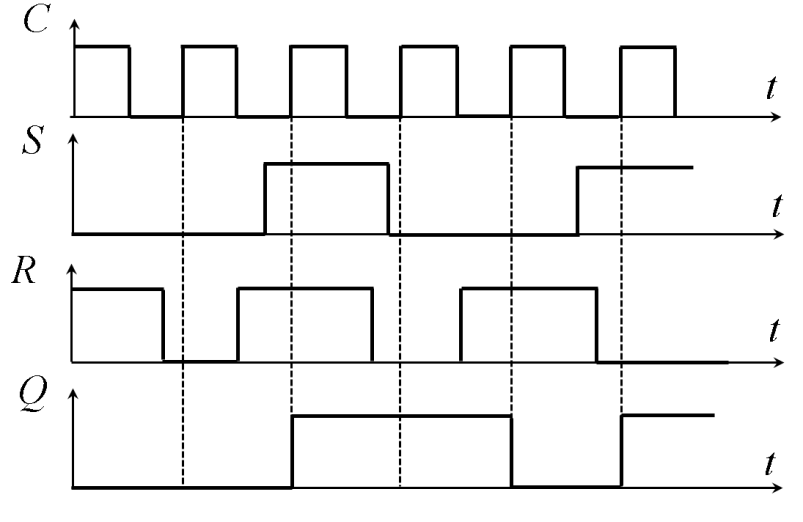

Таблица истинности и временная диаграмма для синхронного RS-триггера, выполненного на элементах И-НЕ, приведены на рис.8. Знак «*» в таблице истинности означает любое состояние.

Рис. 8. Синхронный RS-триггер, выполненный на элементах И-НЕ:

а – таблица истинности, б – временная диаграмма

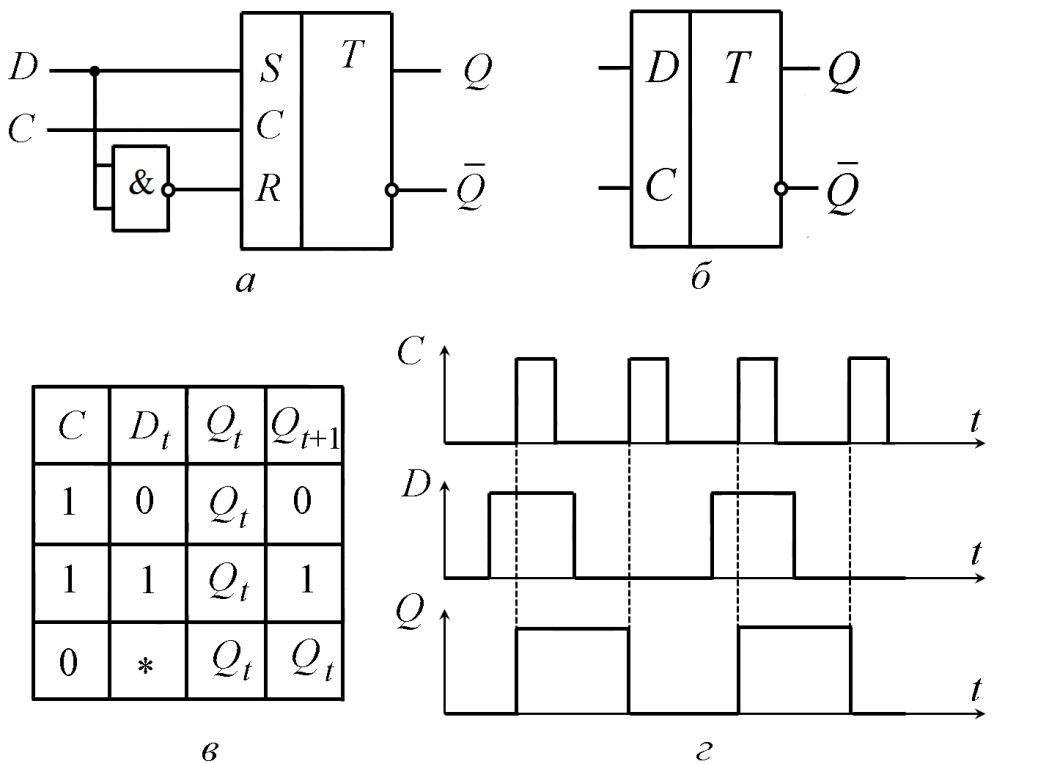

1.3. Синхронный D -триггер

D-триггером называют синхронный триггер, выходное состояние которого совпадает с сигналом на его единственном информационном входе, который тот имел на предыдущем такте импульсов синхронизации.

D-триггер имеет информационный вход D и вход синхронизации С. Одна из возможных структурных схем D-триггера, его условное обозначение, таблица истинности и соответствующая ей временная диаграмма показаны на рис. 10. Если уровень сигнала на входе С равен логическому 0, то состояние триггера устойчиво и не зависит от уровня сигнала на входе D. При подаче на вход С логической 1 информация на прямом выходе будет повторять информацию, подаваемую на вход D .

Рис. 9. Синхронный D-триггер:

а – структурная схема; б – условное обозначение; в – таблица истинности; г – временная диаграмма

Как видно из представленной временной диаграммы в D-триггере происходит задержка сигнала на выходе по отношению к сигналу, подаваемому на вход, на время, не превышающее паузы между синхроимпульсами.

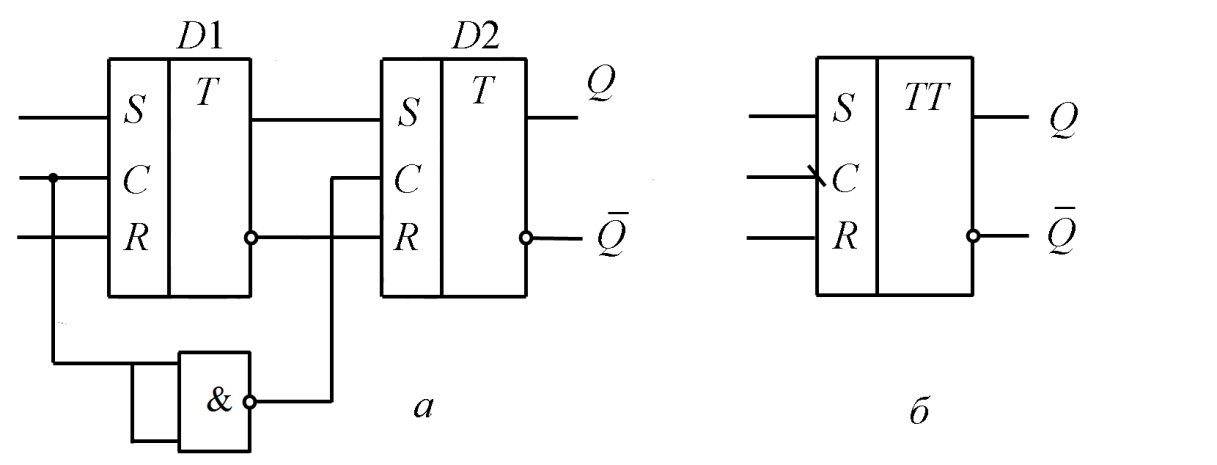

1.4. Двухступенчатый RS -триггер

На рис. 10 приведена структурная схема и условное обозначение триггера, выполненного на двух синхронных RS-триггерах с прямой статической синхронизацией (см. рис. 7, а). Триггер D 1 называют ведущим, а D 2 – ведомым. При нулевом уровне сигнала на С-входе ведущий триггер D 1 блокирован и не воспринимает сигналы, поступающие с информационных входов. При С=1 входная информация записывается в ведущий триггер и соответствующим образом изменяет его состояние. Ведомый триггер при этом блокирован по инверсному С-входу и находится в режиме хранения предыдущего состояния. По окончании импульса синхронизации информация из ведущего триггера D 1 переписывается в ведомый триггер D 2. Таким образом, запись происходит по спаду сигнала синхронизации C (это обозначается наклонной чертой на входе синхронизации в обозначении триггера (см. рис. 10, б)). Двухступенчатые триггеры используются для построения триггеров с динамическими входами.

Рис. 10. Двухступенчатый RS-триггер:

а – структурная схема; б – условное обозначение.

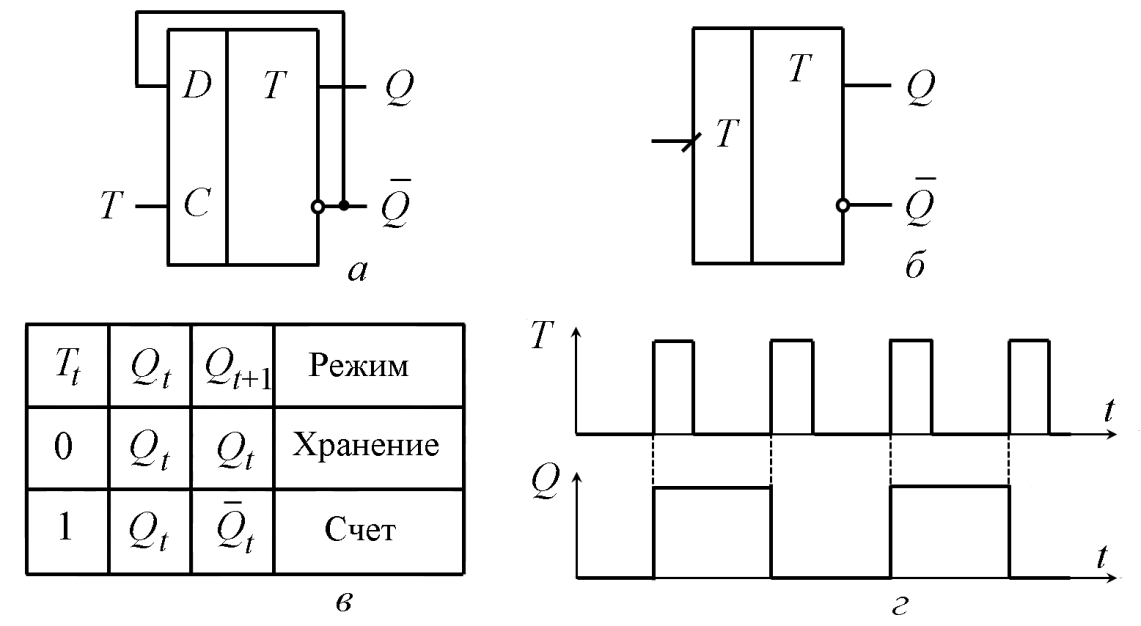

1.5. Счетный Т-триггер

Счетным T-триггером называют триггер, который изменяет свое выходное состояние на инверсное состояние при каждом положительном (или отрицательном) перепаде напряжения на его единственном информационном T-входе.

Структурная схема, условное обозначение, таблица истинности и временная диаграмма Т-триггера, построенного на базе синхронного D-триггера, приведены на рис. 11. При пассивном уровне сигнала на Т-входе (T=0) счетный триггер находится в режиме хранения предыдущего состояния. При положительном перепаде напряжения на входе значение на выходе Q изменяется на противоположное.

Если импульс синхронизации короткий (менее времени переключения триггера) то триггер работает в штатном режиме. При длительном импульсе синхронизации возможен автоколебательный режим.

Как видно из временной диаграммы, частота сигнала на выходе Т-триггера ниже частоты сигнала на входе, поэтому Т-триггер еще называют «делителем частоты».

Рассматриваемый триггер является триггером с динамическим управлением по фронту импульса. Счетный T-триггер с динамическим управлением по срезу импульса можно построить на базе двух последовательно соединенных синхронных RS-триггеров.

Рис. 11. Счетный Т-триггер:

а – структурная схема; б – условное обозначение; в – таблица истинности; г – временная диаграмма

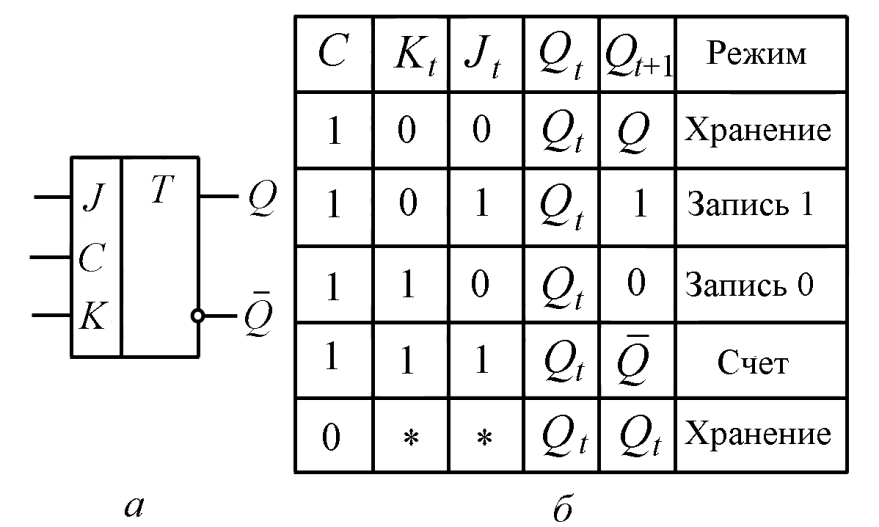

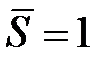

1.6. Универсальный JK -триггер

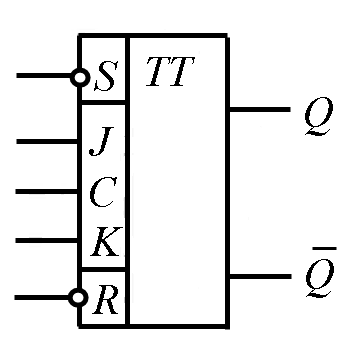

Достоинством универсальных JK-триггеров является возможность при соответствующем включении входов выполнять функции триггеров любого другого типа. В отличие от RS-триггеров JK-триггеры не имеют запрещенных комбинаций входных сигналов. Условное обозначение и таблица истинности синхронного JK-триггера приведены на рис.12, временная диаграмма – на рис. 13. Знак «*» в таблице истинности означает любое состояние. Из таблицы истинности видно, что при подаче на информационные входы J и K сразу двух логических единиц триггер работает как счетный.

Рис. 12. Универсальный JK-триггер:

а– условное обозначение; б – таблица истинности

Рис.13. Временная диаграмма JK-триггера

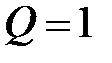

В сериях выпускаемых микросхем существуют также интегральные двухступенчатые JK-триггеры, имеющие дополнительные асинхронные входы (рис.14): предварительной установки S и очистки R триггера. Рабочим для этих входов является низкий уровень напряжения, что показано кружочками у основания входов. При подаче на асинхронные входы двух логических единиц (  ,

,  ) работу триггера контролируют информационные J, K и тактирующий C входы (см. таблицу истинности на рис.12). Если

) работу триггера контролируют информационные J, K и тактирующий C входы (см. таблицу истинности на рис.12). Если  ,

,  , то на выходе устанавливается логическая единица

, то на выходе устанавливается логическая единица  независимо от уровня сигналов на информационных входах, если

независимо от уровня сигналов на информационных входах, если  ,

,  – то

– то  . Одновременная подача на оба асинхронных входа низких уровней сигналов

. Одновременная подача на оба асинхронных входа низких уровней сигналов  запрещена. Кроме того, сигналы на входах J и K не должны меняться, если на тактирующем входе C присутствует напряжение высокого уровня (C=1).

запрещена. Кроме того, сигналы на входах J и K не должны меняться, если на тактирующем входе C присутствует напряжение высокого уровня (C=1).

Рис.14.Интегральный двухступенчатый JK-триггер

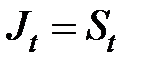

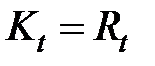

Сравнение таблиц истинности для JK-триггера (см. рис. 12, б) и асинхронного RS-триггера (см. рис. 6, в) показывает, что при условии  и

и  первые три строки этих таблиц полностью совпадают. Поэтому, подавая на К-вход JK-триггера сигнал

первые три строки этих таблиц полностью совпадают. Поэтому, подавая на К-вход JK-триггера сигнал  , а на J-вход сигнал S и исключая запрещенную комбинацию(J=K=1), получим реализацию синхронного RS-триггера на базе JK-триггера.

, а на J-вход сигнал S и исключая запрещенную комбинацию(J=K=1), получим реализацию синхронного RS-триггера на базе JK-триггера.

Подобно Т-триггеру JK-триггер изменяет свое состояние на инверсное предыдущему при активных уровнях сигналов на обоих входах J и K,апри пассивных уровнях сигналов на этих входах находится в режиме хранения. Объединив входы J и K,получим реализацию Т-триггера на базе универсального JK –триггера (рис.16).

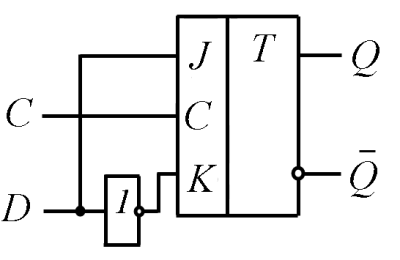

Рис.16. Схема реализации Т-триггера на базе JK-триггера

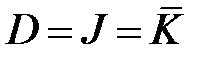

Пример реализации D-триггера на основе универсального JK-триггера приведен на рис.17. Из представленной схемы видно, что при  синхронный JK-триггер будет работать как D-триггер.

синхронный JK-триггер будет работать как D-триггер.

Рис. 17. Схема реализации D-триггера на базе JK-триггера

2. Основы работы в программной среде Multisim

Multisim – это известная программа для математического моделирования и анализа работы электрических и электронных схем. В ней содержатся библиотеки различных компонентов (пассивных элементов, источников, диодов, транзисторов, логических элементов, цифровых микросхем и др.), имеется большой набор контрольно-измерительных приборов (вольтметров, амперметров, осциллографов, плоттер Боде и др.). Среда моделирования MULTISIM имеет удобный графический интерфейс, проста в изучении и практична в работе.

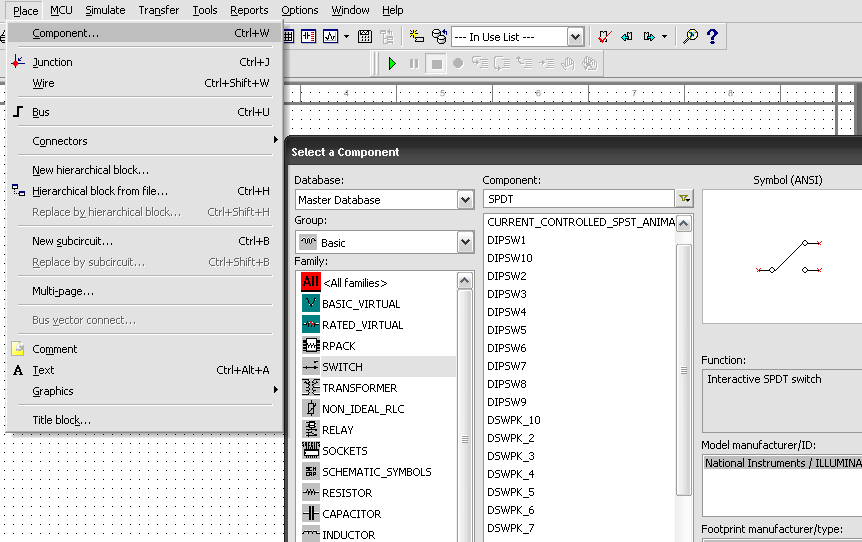

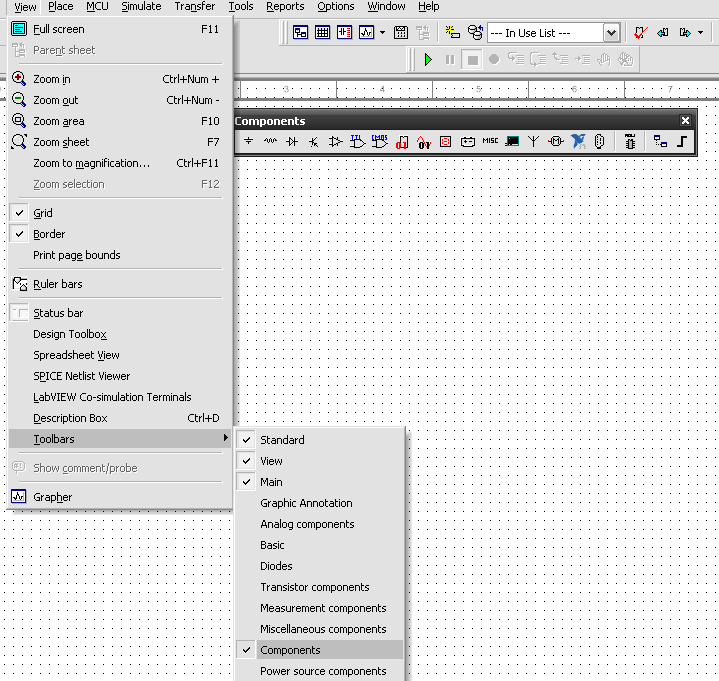

Для создания схем, исследуемых в данной лабораторной работе, понадобятся следующие компоненты: независимый источник питания, «земля», логические элементы, ключ и индикаторные элементы (лампы). Для выбора компонентов на панели инструментов используется вкладка Place , в раскрывшемся меню выбирается вкладка Component (рис.18). Для удобства работы панель Component можно поместить на панель инструментов. Для этого на панели инструментов выбираются вкладки View – Toolbars – Components (рис.19).

Рис. 18. Выбор панели Component на панели инструментов

Рис. 19. Размещение панели Component на панели инструментов

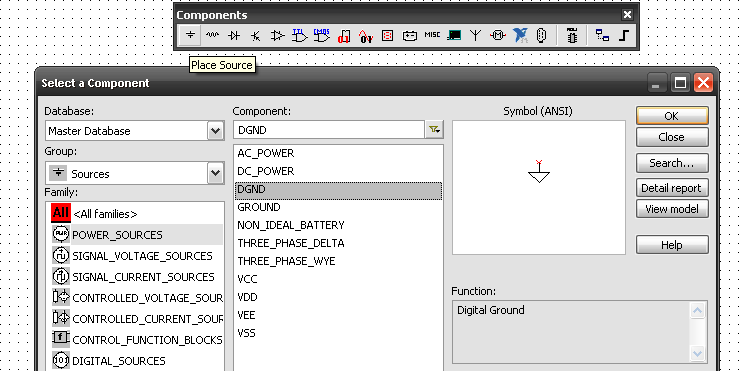

Элемент «земля» находится на панели Components во вкладке Place Source . После открытия вкладки Place Source в диалоговом окне Family выбирается строка POWER SOURCES. Далее в диалоговом окне Component выбирается элемент DGND (рис.20). После нажатия кнопки ОК данный элемент появляется на рабочем поле. Аналогично на рабочее поле помещается независимый источник питания VCC.

Рис. 20. Выбор элемента «земля»

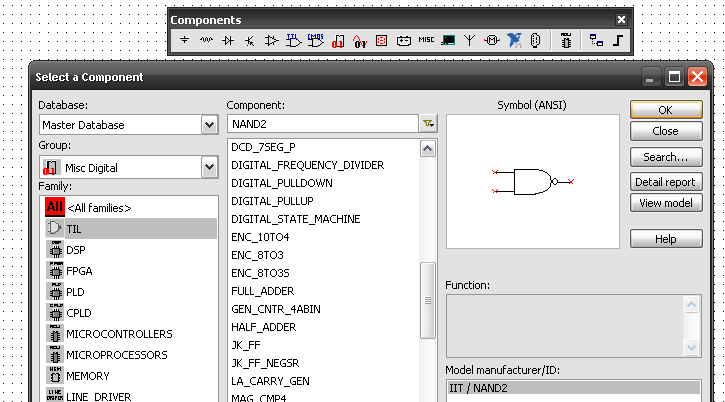

Логический элемент И-НЕ с двумя входами (NAND2) расположен на панели Components во вкладке Misc Digital и семействе TIL (рис.21). Аналогично на рабочее поле помещается логический элемент ИЛИ-НЕ (NOR2).

Рис.21. Выбор элемента И-НЕ

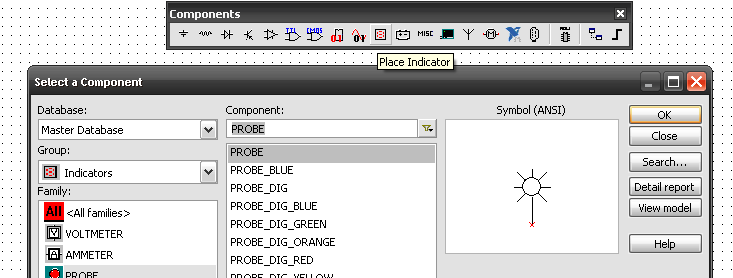

Лампы индикаторы расположены на панели Components во вкладке Indicator и семействе PROBE (рис.22).

Рис. 22. Выбор лампы-индикатора

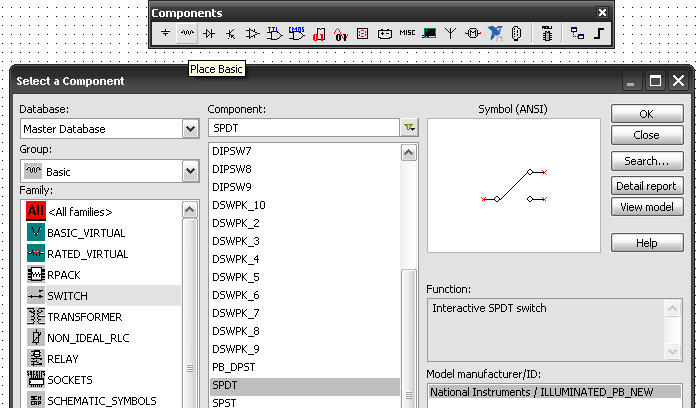

Ключи расположены на панели Components во вкладке Basic и семействе SWITCH (рис.23). В создаваемых схемах необходимо использовать ключ SPDT.

Рис. 23. Выбор ключа

Все элементы схемы можно поворачивать для более удобного и наглядного расположения на рабочем поле. Для этого необходимо навести курсор на элемент, и нажать правую кнопку мышки. Появится меню, в котором надо выбрать опцию Rotate 90 сlockwise для поворота на 90° по часовой стрелке или опцию Rotate 90 counter сlockwise для поворота на 90° против часовой стрелки.

Размещённые на поле элементы соединяются проводами. Для соединения элементов надо подвести указатель мыши к выводу элемента и после появления черной точки, обозначающей соединение, подвести указатель мыши к выводу другого элемента. После соединения элементов можно изменить цвет проводов. Для этого необходимо мышкой щелкнуть по проводу. После появления окна надо щелкнуть на строчку net color и далее выбрать нужный цвет. Для придания проводам промежуточных изгибов, кликните мышкой в местах изгиба.

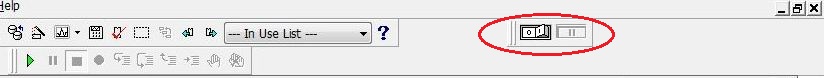

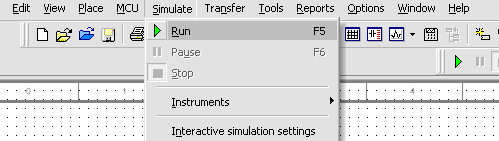

Для анализа работы собранной схемы ее необходимо запустить. Запуск схемы осуществляется либо нажатием клавиши «Simulation switch» (рис.24), либо с помощью команды RUN, которая находится во вкладке Simulate на панели инструментов (рис.25)

Рис. 24. Включение схемы с помощью клавиши «Simulation switch»

Рис. 25. Включение схемы с помощью команды RUN

ЗАДАНИЕ И ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

3.1. Асинхронный RS -триггер на элементах ИЛИ-НЕ

Порядок выполнения задания.

1. Соберите в программном комплексе Multisim схему, представленную на рис. 26.

2. Для собранной схемы заполните таблицу истинности.

| R | S | Q |

| Режим |

| 0 | 0 | |||

| 0 | 1 | |||

| 1 | 0 | |||

| 1 | 1 |

3. Проведите анализ результатов и сформулируйте вывод по заданию.

Примечание:

В приведенной схеме вывод Q 1 соответствует инверсному выводу  (см. рис. 6, б).

(см. рис. 6, б).

При заполнении таблицы истинности необходимо провести тестирование на запрещенное состояние. Для этого триггер устанавливается в состояние отличное от режима хранения и запрещенного состояния. Например, вывод R замыкается на источник +5В (R=1), а вывод S - на землю (S=0). Поочередный выход из этого положения в режимы R=S=1 и R=S=0 позволит сделать вывод о том, какой из режимов является режимом хранения, а какой запрещенным состоянием.

Рис. 26. Асинхронный RS-триггер на элементах ИЛИ-НЕ

3.2. Асинхронный RS -триггер на элементах И-НЕ

Порядок выполнения задания.

1. Соберите в программном комплексе Multisim схему, представленную на рис. 27.

2. Для собранной схемы заполните таблицу истинности.

|

| Q |

| Режим |

| 0 | 0 | |||

| 0 | 1 | |||

| 1 | 0 | |||

| 1 | 1 |

3. Проведите анализ результатов и сформулируйте вывод по заданию.

Примечание:

В приведенной схеме выводы S1, R1 и Q1 соответствуют инверсным выводам  ,

,  и

и  (см. рис. 5, б).

(см. рис. 5, б).

Рис. 27. Асинхронный RS-триггер на элементах И-НЕ

3.3. Cинхронный RS -триггер

Порядок выполнения задания.

1. Соберите в программном комплексе Multisim схему, представленную на рис. 28.

2. Для собранной схемы заполните таблицу истинности.

| C | R | S | Q |

| Режим |

| 1 | 0 | 0 | |||

| 1 | 0 | 1 | |||

| 1 | 1 | 0 | |||

| 1 | 1 | 1 |

3. Проведите анализ результатов и сформулируйте вывод по заданию.

Рис. 28. Cинхронный RS-триггер

Примечание:

В приведенной схеме вывод Q 1 соответствует инверсному выводу  (см. рис. 7, а).

(см. рис. 7, а).

Cинхронный D -триггер

Порядок выполнения задания.

1. Соберите в программном комплексе Multisim схему, представленную на рис. 29.

2. Для собранной схемы заполните таблицу истинности.

| C | D | Q |

| Режим |

| 1 | 0 | |||

| 1 | 1 |

3. Проведите анализ результатов и сформулируйте вывод по заданию.

Рис. 29. Синхронный D-триггер

Примечание:

В приведенной схеме вывод Q 1 соответствует инверсному выводу  (см. рис. 9, б), вывод С используется для подачи тактовых импульсов.

(см. рис. 9, б), вывод С используется для подачи тактовых импульсов.

Двухступенчатый RS -триггер

Порядок выполнения задания.

1. Откройте в программном комплексе Multisim схему, представленную на рис. 30.

2. Для данной схемы заполните таблицу истинности.

| C | R | S | Q |

| Режим |

| 1-0 | 0 | 0 | |||

| 1-0 | 0 | 1 | |||

| 1-0 | 1 | 0 | |||

| 1-0 | 1 | 1 |

3. Проведите анализ результатов и сформулируйте вывод по заданию.

Рис. 30. Двухступенчатый RS-триггер

Примечание:

В приведенной схеме вывод  соответствует инверсному выводу

соответствует инверсному выводу  (см. рис. 10, а), вывод С используется для подачи тактовых импульсов. Для тестирования схемы необходимо на тактирующий вход С подать высокий уровень напряжения (C=1), а на информационные входы – сигналы соответствующие таблице истинности. После этого тактирующий вход С надо перевести в состояние C=0. Это переключение откроет вторую ступень и закроет информационные входы.

(см. рис. 10, а), вывод С используется для подачи тактовых импульсов. Для тестирования схемы необходимо на тактирующий вход С подать высокий уровень напряжения (C=1), а на информационные входы – сигналы соответствующие таблице истинности. После этого тактирующий вход С надо перевести в состояние C=0. Это переключение откроет вторую ступень и закроет информационные входы.

Универсальный JK -триггер

Порядок выполнения задания.

1. Откройте в программном комплексе Multisim схему, представленную на рис. 31.

2. Для данной схемы заполните таблицу истинности.

| C | K | J |

|

| Режим |

| 0-1 | 0 | 0 | |||

| 0-1 | 0 | 1 | |||

| 0-1 | 1 | 0 | |||

| 0-1 | 1 | 1 |

В приведенной таблице  – режим до переключения, – режим после переключения. Для заполнения таблицы истинности необходимо для всех значений выводов J и K проводить измерения для значений

– режим до переключения, – режим после переключения. Для заполнения таблицы истинности необходимо для всех значений выводов J и K проводить измерения для значений  ноль и единица. Т.к. в переходах JK триггера есть неоднозначность. Например, если для значения

ноль и единица. Т.к. в переходах JK триггера есть неоднозначность. Например, если для значения  по результатам измерения для значения

по результатам измерения для значения  получено значение 0. Это может означать два возможных режима: первый – запись 0, второй хранения 0. Для идентификации режима нужно провести измерения при

получено значение 0. Это может означать два возможных режима: первый – запись 0, второй хранения 0. Для идентификации режима нужно провести измерения при  . Если при этом

. Если при этом  1 то это режим хранения, а если при этом

1 то это режим хранения, а если при этом  0 то это режим записи нуля. Начальную установку единицы или нуля для значения

0 то это режим записи нуля. Начальную установку единицы или нуля для значения  устанавливаем по таблице начальной установки (см. ниже Примечание).

устанавливаем по таблице начальной установки (см. ниже Примечание).

Рис. 31. Универсальный JK-триггер

3. Проведите анализ результатов и сформулируйте вывод по заданию. Заполнить таблицу переходов JK триггера исходя из полученной таблицы истинности. Факультативные (безразличные) значения для J и K обозначить символом *.

| Тип перехода | J | K |

| ||

| ||

| ||

|

Примечание:

Представленный JK-триггер имеет два информационных входа J и K. Тактирующий вход С является динамическим с записью по переднему фронту. Для записи необходимо заземлить тактирующий вход и после этого переключить на высокий уровень сигнала (С=1).

Входы с ключами S и R являются управляющими (выводы асинхронной установки начального состояния триггера). Если оба ключа S и R заземлены, то триггер работает в режиме приема сигналов с информационных входов J и К. Если вывод S установлен в состояние 1, а R – в состояние 0, то на выходе JK-триггера установится высокий уровень сигнала (Q=1) независимо от уровня сигналов на информационных входах. Если вывод S установлен в состояние 0, а R – в состояние 1, то на выходе JK-триггера установится низкий уровень сигнала (Q=0) независимо от уровня сигналов на информационных входах. Состояние, при котором оба ключа S и R переключены на высокий уровень напряжения (S=R=1), является запрещенным. Перед установкой информационных входов J, K необходимо управляющие входы переводить в режим приема сигналов (S=R=1).

| S | R | Режим |

| 1 | 0 | Q=1 |

| 0 | 1 | Q=0 |

| 0 | 0 | прием сигналов по выводам J,K и C |

| 1 | 1 | запрещенный режим |

Требования к отчету

Отчет должен содержать:

1) титульный лист;

2) цель работы;

3) схемы триггеров;

4) таблицы истинности;

5) выводы.

Заключение

В данной работе студенты приобретают такие компетенции как способность проводить анализ и синтез соответствующей информации на примерах логических схем синхронных и асинхронных триггеров. Знакомятся с функциональными возможностями асинхронного и синхронного RS-триггерa, D-триггерa, счетного Т-триггера, двухступенчатого RS-триггера, универсального JK-триггера и различными способами хранения информации в них. А также приобретают навыки моделирования триггеров программной среде Multisim.

Вопросы для самоконтроля

1. Какое устройство называют триггером?

2. Как обозначаются различные входы триггеров?

3. Как на практике задают закон функционирования триггера?

4. Какие классификационные признаки триггеров вам известны?

5. В чем принципиальное отличие между работой асинхронного и синхронного триггеров?

6. В чем принципиальное различие между работой триггеров со статическим и динамическим управлением?

7. Какое состояние триггера называют запрещенным?

8. Как практически провести тестирование триггера на запрещенное состояние?

9. В чем принципиальное различие RS-триггеров, построенных на элементах ИЛИ-НЕ и И-НЕ?

10. Сколько и какие входы у D-триггера?

11. В чем принципиальное отличие между функционированием одноступенчатых и двухступенчатых триггеров?

12. Почему Т-триггер называют «делитель частоты»?

13. В чем заключается универсальный характер JK-триггера?

14. Обоснуйте таблицу переходов JK триггера.

15. Объясните назначение входов S, R универсального JK-триггера в последнем задании.

Литература

Основная

1. Бойт К. Цифровая электроника: Пер. с нем. М: Техносфера, 2007. 472с.

2. Браммер Ю.А., Пащук И.Н. Цифровые устройства. М.: Высшая шк., 2004. 229 с.

Дополнительная

1. Марченко А.Л, Освальд С.В. Лабораторный практикум по электротехнике и электронике в среде MULTISIM: учеб. пособие для вузов. М.: ДМК - Пресс, 2010. 448с.

2. Загидуллин Р.Ш. MULTISIM, LabVIEW, Signal Express: Практика автоматизированного проектирования электронных устройств. М.: Горячая линия - Телеком, 2009. 366с.

3. Токхейм Р. Основы цифровой электроники: Пер. с англ. М.: Мир, 1988. 392 с.

Дата добавления: 2019-02-22; просмотров: 828; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!