Принципиальная схема отдельных блоков

ЛАБОРАТОРНАЯ РАБОТА №2

СХЕМА СТЕНДА И С-КОМПИЛЯТОР

Цель работы – освоение основных принципов построения микропроцессорных систем на базе микроконвертера ADuC812 и разработки программ на языке С для него.

В процессе работы необходимо изучить:

- аппаратную часть:

· функциональную схему стенда SDK-1.1:

* организацию шин;

* особенности архитектуры;

* принцип работы с внешними устройствами;

* карту адресного пространства стенда;

· принципиальную схему отдельных блоков стенда;

- компилятора языка С фирмы Keil Software:

· модели памяти;

· указатели;

· типы данных.

ТЕОРЕТИЧЕСКАЯ ЧАСТЬ

Функциональная схема стенда SDK-1.1

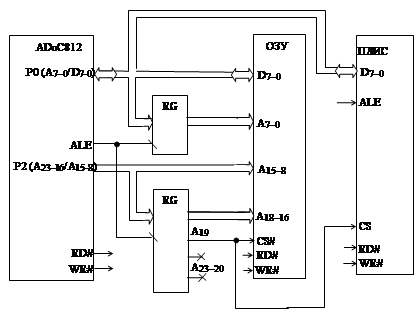

Из структурной схемы стенда (см. лаб. работу №1) видно, что внешняя оперативная память (ОЗУ) и ПЛИС подключаются к системной шине микроконвертера. Системная шина включает в свой состав три функциональные шины: 8-разрядную шину данных (D7– 0), 24-разрядную шину адреса (А23–0) и шину управления. У микроконвертера ADuC812 для формирования шины данных и шины адреса отведено всего два 8-разрядных порта: порт Р0 и порт Р2, которые используются в режиме мультиплексирования для формирования полноразрядных шин. Порт Р0 служит выходом мультиплексированной шины адрес/данные (А7-0/D7-0), а порт Р2 – шины адрес/адрес (А23-16/А15-8). Мультиплексирование применяется с целью уменьшения числа выводов у корпуса процессора, отводимых под эти шины. Для демультиплексирования (разделения) шин у микроконвертера введен дополнительный управляющий сигнал ALE, и, кроме того, введены внешние регистры адреса. На рис.2.1 приведена функциональная схема формирования шин адреса и данных, а также схема подключения к ним ОЗУ и ПЛИС.

|

|

|

Рис.2.1. Схема формирования шин адреса и данных и подключения к ним ОЗУ и ПЛИС

В начальный момент времени процессор выставляет на шину адрес/данные (А7-0/D7-0) адрес А7-0,а на шину адрес/адрес (А23-16/А15-8) адрес А23-16 и формирует сигнал ALE, по которому младший А7-0 и старший А23-16 байты адреса записывается в соответствующие внешние регистры. На второй стадии процессор использует шину адрес/данные (А7-0/D7-0) в качестве шины данных D7-0, а шину адрес/адрес (А23-16/А15-8) для передачи среднего байта адреса А15-8. Направление передачи по шине данных задается при помощи сигналов шины управления: записи или чтения (WR#, RD#).

У микроконтроллеров семейства MCS-51 подключение внешних устройств к системной шине осуществляется по принципу "общей шины". Это означает, что они включаются в адресное пространство внешней памяти данных контроллера. Таким образом, внешние устройства, подключаемые к системной шине через ПЛИС, и внешняя память данных находятся в едином адресном пространстве. Адресное пространство внешней памяти данных микроконтроллера составляет 16Мбайт. Стенд SDK-1.1 имеет внешнюю память емкостью 512Кбайт, на которую необходимо завести 19 линий адреса 219=512К (А18 – А0). Следовательно, для разделения адресного пространства между памятью и ПЛИС можно использовать линию адреса А19: подключить ее к входам CS # ОЗУ (активизирует ОЗУ, когда на нем лог."0") и CS ПЛИС (активизирует ПЛИС, когда на нем лог. "1") (рис.2.1).

|

|

|

Микроконтроллеры семейства MCS-51 построены по гарвардской архитектуре, т.е. память программ и память данных располагаются в разных адресных пространствах. Для возможности подключения к внешним шинам адреса и данных этих двух видов памяти в шине управления имеются соответствующие сигналы: PSEN# - сигнал выбора команд из памяти программ, RD# и WR# - чтение и запись для обмена информацией с памятью данных. Так как стенд SDK-1.1 предназначен для использования в учебных целях, то это накладывает свои особенности на построение всей системы. В частности, в процессе проведения лабораторных работ приходится периодически перезагружать управляющую программу. Ежедневная многократная перезагрузка наиболее просто реализуется при помещении управляющей программы в ОЗУ. Следовательно, необходимо изменить структуру системы, диктуемую MCS-51, а именно – поместить память программ и память данных в единое адресное пространство. Это можно реализовать путем объединения сигналов PSEN# и RD#.

|

|

|

На рис.2.2 представлена общая функциональная схема стенда. Объединение сигналов PSEN# и RD# выполнено при помощи схемы "И". Чтобы не выйти за адресное пространство памяти программ (напомним, что память программ микроконвертера составляет 64К) при выборке внешних команд, сигнал PSEN# заведен также и на вход сброса регистра адреса RG2.

Внешние устройства, управляемые через системную шину, подключены к ней через программируемую логическую интегральную схему (ПЛИС). На ПЛИС реализована схема интерфейса внешних устройств с шиной. Использование ПЛИС упрощает подключение внешних устройств, экономит элементную базу, позволяет просто модернизировать схему путем ее перепрограммирования. Выбор между памятью и внешними устройствами (ПЛИС) осуществляется при помощи адресной линии А19, которая заводится на входы выбора ОЗУ и ПЛИС. При А19=0 активизируется ОЗУ, при А19=1 – ПЛИС, т.е. физический адрес ПЛИС начинается с 0x80000h, что соответствует восьмой странице памяти.

|

|

|

С целью экономии выводов ПЛИС на нее вместо трех линий адреса с регистра адреса (А2, А1, А0) заведен сигнал ALE. Таким образом, в ПЛИС также должен быть реализован регистр адреса, аналогичный регистру RG1. На ПЛИС должны быть реализованы схемы дешифрации адреса и порты (регистры) ввода-вывода. Сигналами RD#, WR# информация или читается с порта ввода в процессор, или записывается в порт вывода из процессора. К ПЛИС подключены:

• клавиатура;

• ЖКИ;

• линейка светодиодов;

• звуковой излучатель;

• 16 дискретных портов ввода-вывода.

Аналоговые входы заведены на АЦП микроконвертера через делитель напряжения с целью расширения динамического диапазона входных сигналов (обработка сигналов большего напряжения).

Рис.2.3. Карта адресного пространства стенда SDK-1.1

Источник питания представляет собой последовательно включенные диодный мост, фильтр, два стабилизатора, диод и ионистор. Второй стабилизатор имеет выход +3,3В для питания ПЛИС. Ионистор заряжается через диод во время работы стенда, и в то же время, при отключении стенда от питающей сети, диод позволяет ионистору обеспечивать питание только часов реального времени.

Карта адресного пространства стенда представлена на рис.2.3. Из карты видно, что пространство памяти программ, относящееся к внешней памяти, физически помещено во внешнюю память данных. Поэтому в настройках проекта необходимо указать начальные адреса внешней памяти программ и внешней памяти данных (см. лаб. раб №1), с тем, чтобы они не пересеклись в общей памяти. Пунктиром отмечена отсутствующая память. На рисунке указаны сигналы, при помощи которых осуществляется доступ к той или иной области памяти.

Принципиальная схема отдельных блоков

Принципиальная схема прикладывается к стенду SDK-1.1. Далее все обозначения элементов, приведенные на рисунках, соответствуют обозначениям принципиальной схемы.

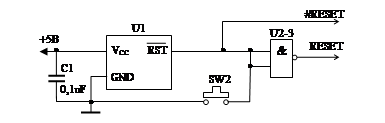

Схема сброса

Схема сброса (рис.2.4) предназначена для формирования качественного сигнала RESET после включения питания, после нажатия кнопки RESET или после скачка (провала) питания. Проблема состоит в том, что при старте контроллера после включения питания или при скачке питания возможны различные переходные процессы, которые могут привести к некорректному исполнении программ или порче содержимого ОЗУ.

Супервизор питания (U1) DS1813 обеспечивает формирование сигнала RESET длительностью 150 мс, т.е. на время, достаточное для окончания всех переходных процессов.

Рис.2.4. Схема сброса

Источник питания

Переменное (15..16В) или постоянное (9..10В) напряжение от внешнего источника питания попадает на диодный мост U15 через разъем J4. Сердцем встроенного в SDK 1.1 источника питания (рис.2.5) является микросхема LM7805C. Эта микросхема является интегральным стабилизатором с защитой от перегрева и короткого замыкания. Она обеспечивает выходное напряжение +5В ± 2%, выходной ток до 1 А.

Рис.2.5. Источник питания

Стабилитрон D19 (1N4745A) предназначен для защиты LM7805C и электролитических емкостей от повышенного входного напряжения (напряжения пробоя стабилитрона 16В).

Электролитические конденсаторы C35, C36 и С38 необходимы для сглаживания пульсаций входного напряжения. Они подавляют низкочастотные помехи, проникающие в систему по цепи питания. Так как электролитические конденсаторы имеют большую внутреннюю индуктивность, то они не подавляют высокочастотные помехи. Кроме того, они поддерживают работоспособность SDK-1.1 при кратковременных пропаданиях напряжения питания. Устанавливать конденсаторы следует как можно ближе к контактам разъема.

Емкости C40 и C37 необходимы для фильтрации высокочастотных помех. В качестве них обычно используют керамические конденсаторы емкостью 0,1мкФ.

Напряжение 3,3В для питания ПЛИС формируется с помощью стабилизатора U10 (LD1117S) (рис.2.6).

Рис.2.6. Стабилизатор на 3,3В

Фильтрующие емкости

Фильтрующие емкости (рис.2.7) равномерно распределены по всей поверхности печатной платы. Каждый конденсатор соединяет плюс питания с корпусом. Фильтрующие емкости шунтируют высокочастотные помехи, возникающие в цепях питания 3,3 и 5В.

Рис.2.7. Фильтрующие емкости

Шунтирование происходит из-за того, что активное сопротивление емкости тем меньше, чем выше частота сигнала.

XC = 1∕(2πƒC) ,

где XC – активное сопротивление конденсатора; ƒ – частота; C – емкость. Для постоянного напряжения сопротивление конденсатора близко к бесконечности, а для переменного напряжения высокой частоты конденсатор является резистором с низким сопротивлением.

Кварцевые резонаторы

Кварцевые резонаторы - устройства, использующие пьезоэлектрический эффект для возбуждения электрических колебаний заданной частоты. При совпадении частоты приложенного напряжения с одной из собственных механических частот кварцевого вибратора в приборе возникает явление резонанса, приводящее к резкому увеличению проводимости.

Обладая среди резонаторов самой высокой добротностью Q~105–107 (добротность колебательного LC-контура не превышает 102, пьезокерамики – 103), кварцевые резонаторы имеют также высокую температурную стабильность и низкую долговременную нестабильность частоты (106..108). Кварцевые резонаторы применяются в генераторах опорных частот, в управляемых по частоте генераторах, селективных устройствах: фильтрах, частотных дискриминаторах и т.д.

В SDK-1.1 два кварцевых резонатора. Y1 служит для тактирования ADuC812 (12,0 МГц), а Y2 – для тактирования часов реального времени (32,768 КГц).

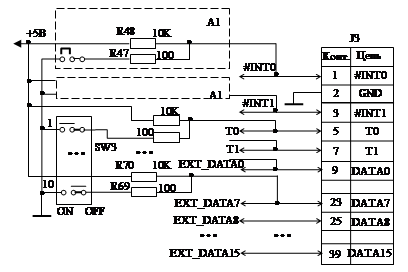

Дискретные входы-выходы

Дискретные входы-выходы предназначены для ввода и вывода информации, представленной в двоичном виде. Сигнал на входе или выходе дискретного порта может принимать значение логического нуля или единицы.

Рис.2.8. Дискретные входы-выходы

В SDK-1.1 дискретные порты выведены на разъем J3 (рис.2.8). Эти порты можно использовать для подключения модулей SDX или каких-либо других внешних устройств. Кроме этого, к дискретным входам/выходам подключены DIP переключатели SW3, позволяющие задавать фиксированные значения сигналов на входах. По умолчанию все входы притянуты к логической единице (через резисторы на +5В). При замыкании переключателя SW3 на выбранном входе появляется логический ноль.

Дискретные входы/выходы не имеют гальванической изоляции. Логическому нулю соответствует 0В, а логической единице +5В (уровни TTL). Нагрузочная способность дискретных портов ввода-вывода, подключенных к разъему J3, невелика, так как на разъем выведены порты ADuC812 без каких-либо дополнительных усилителей.

Регистры

Регистры-защелки U3 и U7 используются для демультиплексирования шин адреса и данных. В качестве восьмиразрядного регистра-защелки используется микросхема 74HCT73W.

Положительный перепад на входе CLK приводит к запоминанию состояния входов D1..D8 и выдаче информации на выходы Q1..Q8. Активный уровень на входе CLR (логический «0») приводит к обнулению содержимого регистра-защелки. Регистры-защелки фиксируют данные по сигналу ALE. Таблица истинности 8-разрядного регистра-защелки 74HCT73W приведена ниже.

Таблица 2.1

| Входы ( INPUTS ) | Выход ( OUTPUT ) | ||

| CLR (RESET) | CLK (CLOCK) | Dn (DATA) | Qn |

| L | X | X | L |

| H | ↑ | H | H |

| H | ↑ | L | L |

| H | L | X | Q0 |

В U3 попадает младшая часть адреса (A0..A7), в U7 – старшие 4 бита адреса (A16..A19). Бит A19 используется как сигнал CS (Chip Select) для выбора микросхемы ОЗУ. ОЗУ выбирается, если на A19 логический ноль. При наличии логической единицы на A19 выбирается ПЛИС.

На схеме SDK-1.1 изображены две микросхемы статической памяти: KM684000 и AS7C4096. Обе микросхемы являются микросхемами статической памяти с организацией 512Кx8 (512 Кбайт). На самом деле в стенд SDK-1.1 запаивается только одна из микросхем. У микросхемы U5 «перепутаны» адресные линии. Это не ошибка, а специальный прием, применяемый при проектировании печатных плат и позволяющий упростить разводку проводников.

Дата добавления: 2019-02-12; просмотров: 278; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!