Rвых - состояние шины разрешения чтения.

Исследование работы последовательного регистра.

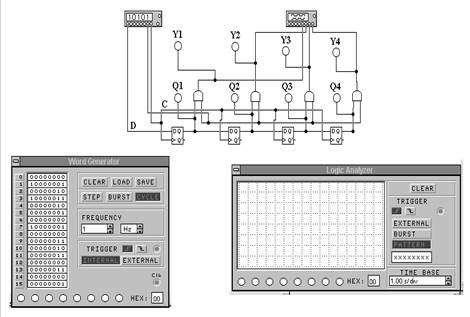

Аналогично предыдущей задаче вызвать и развернуть из каталога «Lab» файл «poslreg». В результате этого в рабочем окне пакета появится схема, представленная на Рис.3.

Рис3 Схема для исследования логических cвойств последовательного регистра.

Запустить эту схему вначале в циклическом, а затем в шаговом режиме. По результатам исследовентй работы регистра заполнить содержанте таблицы 3 для всех состояний управляющего слова:

11

дешифратором по четырем адресным входам (А1, А2, А3. А4).Управление каналом выхода производится сигналом Суп.

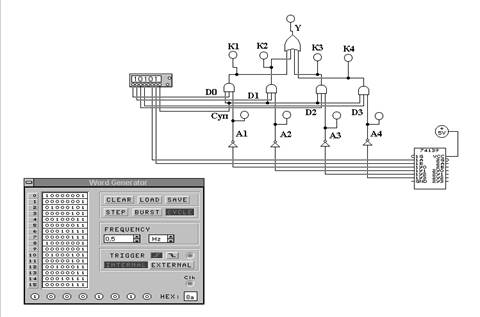

Рис.7 Схема для исследования логических cвойств мультиплексора.

Таблица 8

| Состояние каналов ввода | Код дешифрарора | Разрешение вывода Суп | Состояние каналов вывода | Выход Y | |||||||

| D0 | D1 | D2 | D3 | А | В | К1 | К2 | К3 | К4 | ||

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | |||||

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | |||||

| 0 | 1 | 0 | 0 | 1 | 0 | 1 | |||||

| 0 | 0 | 0 | 0 | 1 | 0 | 1 | |||||

| 0 | 0 | 1 | 0 | 0 | 1 | 1 | |||||

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | |||||

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | |||||

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | |||||

|

10

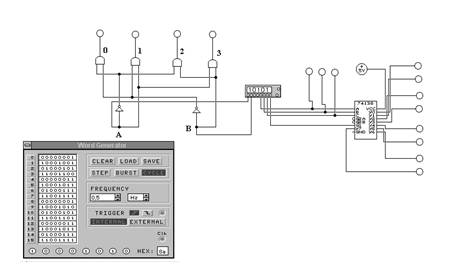

Рис.6 Схема для исследования логических cвойств дешифратора.

|

|

|

Таблица 7

| Код входа | Номер активного выхода | ||||||||||

| С | В | А | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | |

| 0 | 0 | 0 | |||||||||

| 0 | 0 | 1 | |||||||||

| 0 | 1 | 0 | |||||||||

| 0 | 1 | 1 | |||||||||

| 1 | 0 | 0 | |||||||||

| 1 | 0 | 1 | |||||||||

| 1 | 1 | 0 | |||||||||

| 1 | 1 | 1 | |||||||||

Исследование работы мультиплексора.

Аналогично предыдущей задаче вызвать и развернуть из каталога «Lab» файл «multipl». В результате этого в рабочем окне пакета появится схема, представленная на Рис.7. В структуру этой схемы включен дешифратор на четыре входных канала (D0, D1, D2, D3,), который управляется

7

Таблица 3

| Состояние регистра на входе | Содержание регистра | ||||

| C | D | Q1 | Q2 | Q3 | Q4 |

Где: C - состояние тактового входа регистра;

|

|

|

D - состояние цифрового входа первого триггера регистра.

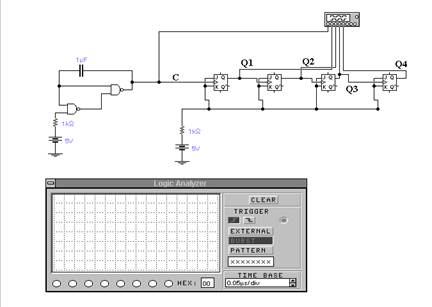

Исследование работы двоичного счетчика.

|

Аналогично предыдущей задаче вызвать и развернуть из каталога «Lab» файл «schetch». В результате этого в рабочем окне пакета появится схема, представленная на Рис.4. Счетчик состоит из четырех последовательно соединенных универсальных триггеров типа «J-K», на счетный вход первого из них подается тактовый импульс «С».

Рис.4 Схема для исследования логических cвойств двоичного счеичика.

8

Запустить эту схему вначале в циклическом, а затем в шаговом режиме. По результатам исследовентй работы счеичика и показаниям логического анализатора заполнить содержанте таблицы 4 до полного заполнения триггеров счеичика.

Таблица 4

| 1-й цикл счета | 2-й цикл счета | 3-й цикл счета | 4-й цикл счета | 5-й цикл счета | 6-й цикл счета | 7-й цикл счета | 8-й цикл счета | |||||||||

| C | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| Q1 | ||||||||||||||||

| Q2 | ||||||||||||||||

| Q3 | ||||||||||||||||

| Q4 | ||||||||||||||||

|

|

|

Где: C - состояние тактового входа счетчика;

Q1 – Q4 - состояние триггеров счетчика.

Исследование работы шифратора.

|

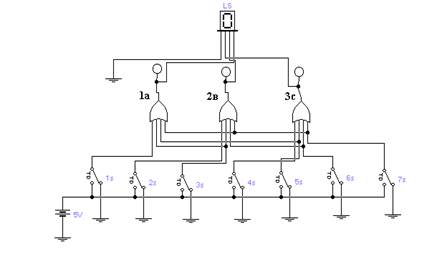

Аналогично предыдущей задаче вызвать и развернуть из каталога «Lab» файл «shifrat3». В результате этого в рабочем окне пакета появится схема, представленная на Рис.5.

Рис.5 Схема для исследования логических cвойств шифратора.

9

Запустить эту схему и проследить ее работу по показаниям индикаторов и положению переключателей, подающих единтчный или нулевой сигнал на соотведствующте входы логических элементов «ИЛИ». По результатам исследовентй работы шифратора дополнить содержание таблицы 5.

Таблица 5

| Номера входов шифратора | Двоичный номер входа | ||||||||

| 1s | 2s | 3s | 4s | 5s | 6s | 7s | 3с | 2в | 1а |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

|

|

|

Дата добавления: 2018-11-24; просмотров: 95; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!