Сумматоры комбинационного типа.

Накапливающие сумматоры могут строиться двумя способами:

с использованием счётных триггеров;

по структуре “комбинационный сумматор плюс регистр хранения”.

Первый способ в настоящее время практически не применяется вследствие двухтактности операции сложения, низкой скорости распространения сигналов переноса и сложности управления сумматором.Во втором случае можно реализовать две схемы:

с запоминанием результата операции “S: = А плюс В”;

с накоплением результата “S: = S плюс А”.

На рис. 11 приведена схема 4-разрядного параллельного накапливающего сумматора, выполненного по структуре “комбинационный сумматор плюс регистр хранения” (на часть схемы, нарисованную штриховой линией пока не обращайте внимания). Число с выхода регистра подаётся на входы В сумматора, поэтому здесь реализуется микрооперация “S: = S плюс А”.

Термин “делитель частоты” указан в кавычках, чтобы подчеркнуть тот факт, что выходные импульсы расставляются им неравномерно (равномерная расстановка импульсов обеспечивается только для значений А, являющихся степенью двойки). Временные диаграммы для рассматриваемой схемы при различных значениях А приведены на рис. 12.

Кроме использования сумматоров по их прямому назначению, они широко применяются при построении самых различных схем, узлов и операционных блоков. Сумматор является ядром арифметическо-логического устройства (АЛУ), выпускаемого в виде специализированной ИС, причём само АЛУ является ядром процессорных элементов. Чрезвычайно широкое применение находят четвертьсумматоры (элементы “сумма по модулю 2”), реализуемые во многих сериях. Отметим ещё несколько примеров использования сумматоров: двоично-десятичные сумматоры, инкременторы и декременторы, цифровые матричные умножители, цифровые фильтры, преобразователи кодов, счётчики и пересчётные устройства, пороговые схемы, линейные цифровые автоматы и др.

|

|

|

Более подробные сведения о рассмотренных и других структурах сумматоров и схемах на их основе можно получить из многочисленных публикаций, в частности [2–10].

Арифметико-логические устройства.

Арифметико-логические устройства АЛ У (ALU, Arithmetic-Logic Unit) выполняют над словами ряд действий. Основой АЛ У служит сумматор, схема которого дополнена логикой, расширяющей функциональные возможности АЛ V и обеспечивающей ею перестройку с одной операции на другую

Обычно АЛУ четырехразрядны и для наращивания разрядности объединяются с формированием последовательных или параллельных переносок. Логические возможности АЛУ разных технологий (ТТЛШ, КМОП, ЭСЛ) сходны. В силу еа м од вой сг ве н н ости выполняемых операций условное обо значение и таблица истинности АЛУ встречаются в двух вариантах, отличающихся взаимно инверсными значениями переменных.

|

|

|

АЛУ (рис. 2.35) имеет входы операндов А и В, входы выбора операции S, вход переноса Ci и вход М (Mode), сигнал которого задает тип выподняемых операций: логические (М = 1) или арифметико-логические (N1 =0). Результат операции вырабатывается на выходах F, выходы G и Н дают функции генерации и прозрачности, используемые для организаций параллельных переносов при наращивании размерности АЛУ. Сигнал Со - выходной перенос, а выход А - В есть выходсравнения на равенство с открытым коллектором.

Перечень выполняемых АЛУ операций дан в табл. 2.13. Для краткости двоичные числа S_1S2S]S0 представлены их десятичными эквивалентами. Под утолщенными обозначениями 1 и 0 следует понимать наборы 1111 и 0000, входной перенос поступает в младший разряд слова, т. е. равен 00ОС,- Логические операции поразрядные, т. е. операция над словами А * В означает, что а, * Ь, при отсутствии взаимовлияния разрядов. При арифметических операциях учитываются межразрядные переносы.

Шестнадцать логических операций позволяют воспроизводить все функции двух переменных. В логико-арифметических операциях встречаются и логические и арифметические операции одновременно.

|

|

|

Запись типа А\/В + АВ следует понимать так: вначале поразрядно выполняются операции инвертирования (В), логического сложения (А\/В) и умножения (АВ), а затем полученные указанным образом два четырехразрядных числа складываются арифметически.

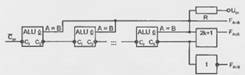

При операциях над словами большой размерности АЛУ соединяются друг с другом с организацией последовательных (рис. 2.36, с) или параллельных (рис. 2.36, б) переносов. В последнем случае совместно с АЛУ применяют микросхемы — блоки ускоренного переноса (CRU, Carry Unit), получающие от отдельных АЛУ функции генерации и прозрачности, а также входной перенос и вырабатывающие сигналы переноса по формулам, приведенным в предыдущем параграфе.

Схемы наращивания АЛУ григюследоеагельном (в) и параллельном (б) переноса* и реализация функций компаратора для фуппы АЛУ (в)

В состав АЛУ входит сумматор, регистры, в которых хранится информация в ходе выполнения операций и образуются результаты вычислений, и логические схемы, осуществляющие необходимые преобразования информации. Арифметико-логическое устройство в зависимости от выполнения функций можно разделить на две части:

|

|

|

1) микропрограммное устройство (устройство управления), задающие последовательность микрокоманд (команд);

2) операционное устройство (АЛУ) , в котором реализуется заданная последовательность микрокоманд (команд). Часть операционных регистров является программно-доступной, то есть они могут быть адресованы в команде для выполнения операций с их содержимым. К ним относятся :

1) сумматор,

2) индексные регистры,

3) некоторые вспомогательные регистры.

остальные регистры программно-недоступные, так как они не могут быть адресованы в программе . Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу обработки информации и логической структуре. Сложность логической структуры АЛУ в определенной степени можно охарактеризовать количеством отличающихся друг от друга микроопераций, необходимых для выполнения всего комплекса задач, поставленных перед АЛУ. На входе каждого регистра собраны соответствующие логические схемы, обеспечивающие такие связи между регистрами, что позволяют реализовать заданный набор микроопераций. Выполнение операций над словами сводится к выполнению последовательности микрокоманд, которые управляют передачей слов в АЛУ и действиями по преобразованию слов. Порядок выполнения микрокоманд определяется алгоритмом выполнения операций. Следовательно, связи между регистрами АЛУ и функции, которые должны выполнять регистры, зависят в основном от принятой методики выполнения операций : арифметических, логических и специальной арифметики.

Дата добавления: 2018-05-31; просмотров: 477; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!