Параллель тасмалдауы бар параллель сумматорлар. Параллель тасмалдауды ұйымдастыру үшін арнайы арналған түйіндер-тез тасмалдау болктары қолдынылады

Параллель тасмалдауды ұйымдастыру үшін арнайы арналған түйіндер-тез тасмалдау болктары қолдынылады. Жеделдетіп тасмалдау принципін мынада: әр бір екі разрядқа қосымша екі сигнал арналған:

G —тасмалдау құружәнеH — тасмалдау таралуы.

GI = aI·bI

HI = aI + bI

GI=1болған жағдайды,яғниaI=bI=1, бұл берілген i-разрядта келесі жоғарғы разрядқаPI+1 алмасусигналы алдынғы разрядтағы функциялардың қосындысына тәуелсіз қалыптасады .

Егерде aI немесе bI «1»тең болса ,яғни HI=1 тең болса,келесі разрядқа бастапқы разрядтан алмасу сигналы болғанда ғана көшірледі.

Егерде GI=1,яғни aI=bI=1,алдынғы разрядтарға қосындылардың қалыптасуына тәуелсіз, i-разрядта келесі жоғарғы разрядқа апаратын PI+1тасмалдау сигналы қалыптастырылады.

Егерде қосындылардың біреуі aI немесеbI,«1» тең болса, яғниHI=1. Келесі разрядқа тасмалдау тек қана сигал болғанда ғана іске асырылады.

Егерде HI=HI–1=1 және PIалдынғы i-ші разрядтан алмасу сигналы болса онда көшіру i+2 разрядқа істеледі

Жалпы жағдайда үдемелі ауысу үрдісін қалыптастыру мына теңдеумен беріледі:

PI+1 = GI + HI·GI–1 + HI·HI–1·GI–2 + … + HI·HI–1·…·H2·H1·P1

Тез тасмалдау блоктары интегралдық түрде орындалған жеке микросхема немесе сумматор сұлбасымен немесе бір микросхемада арифметика-логикалық құрылғы түрде шығарылады.

|

|

|

7.1.3 арифметика-логикалық құрылғы

Негізгі арифметикалық амалдарға қосу және алу жатады. Алу амалдарын қосу әдісмен орындау үшін кері және қосымша кодтар жасалған. Алу амалын орындау үшін, азайтқышты қосымша кодқа өткізіп бірінші қосылғышқа қосу керек.Алынған нәтижені қосымша кодта көрсетілген. Оны сосын тікелей кодқа өткізу керек.Оң сандардың тікелей және кері кодтары бірдей.Теріс сандарды косымша кодқа айналдырғанда,барлық разрядтарын тура кодтың инверсия жасап және кіші разрядына бірді қосу керек. Қосымша кодты тікелей кодқа айналдырғанда,алынған нәтижені инверсия жасап кіші разрядқа бірді қосу керек.Сонымен қосу әдісімен алу амалы қосымша уақыт шығымын қажет етеді және есептеу құрлғылардың жылдамдығын азайтады.

ЭЕМ жылдамдығын өсіру үшін , арифметикалық және логикалық амалдарды түрлендірмей сандардың тікелей кодтарымен орындауды қамтамасыз ететін, құрамдастырылған арифметико-логикалық құрылғылар істелген және қолдынылады.

|

|

|

Қосу және алу амалдарын орындау үшін , бір разрядты арифметикалық құрылғылардың істеу әдістері 25 суретте көрсетілген.

Қосу және алу амалдарының логикалық өрнектерін салыстырғанда, қосу(25,а сурет) және алу(25,б сурет) амалдарының өрнектері бір бірне сәйкес келеді,ал қарызға алу өрнегі қосу және алу амалдарының бөлігі болып табылады.

25 сурет.Ақиқат кестсі және құрылым формулалары қосу а),алу б) және бір разрядты АЛҚ сұлбасы в).

Сонымен алу амалын орындау үшін қосымша сигналдар алудың қажетілігі жоқ,қосымша аппаратық шығымдар керек болмайды.операцияның коды сәйкес көшіру және қарызға алу сигналдарын комутациялауын қамтамасыз өткізу қажет.

25, в) суретте U кернеуінен келетін екі әр полярлы сигналмен басқару ісін орындайтын орындайтын басқару құрылғысы ролін екі клапанды қарапайым АЛҚ сұлбасы келтірілген.. 25суреттте сұлбаның бұл бөлігі пунктир сызықпен белгіленген. U=0 болғанда алу амалы орындалады, ал U=1— қосу амалы орындалады. 25, в) суретінде

Басқару кернеуінен U әрполярлы сигналдармен басқарылатын

|

|

|

Көпразрядты АЛҚ интегралдық микросұлба түрінде шығарылады немесе процессордың негізі болып оның құрамына кіреді. МС 564ИП3 (26,а сурет) —бұл 16 арифметикалық және 16 логикалық операциялар жасайтын төртразрядты параллель АЛҚ

26сурет.4-разрядтыАЛУ564ИП3 сұлбасыа)564ИП4тездетіп тасмалдау сұлбасы б).

A(а0–а3) — бірінші операнд,

B(b0–b3) — екінші операнд,

S(s0–s3) — операция коды — 4 разрядты.

Егер M=0, онда арифметикалық амалдар орындалады: 24=16,M=1 болғанда логикалық операциялар орындалады: 24=16. Барлығы 16+16=32 операция.

F(f0–f3) —операция нәтижесі. A=B шығысында «1»пайда болады,егер азайту амалын орындағанда операцияның нәтижесі «0»тең болса , яғни A=B.

АЛҚ параллель типті болғандықтан оның G генерация шығысыжәне H тасмалдау таралуы бар. Pn және Рn+ -шығатын және кіретінтасмалдар.

Тізбектей тасмалдайтын параллель сумматордағы дай, МС АЛҚ өңдейтін сөздердің разрядтығын үлкейту үшін оны тізбектеп қосуға болады.Бұл жағдайда операция орындау уақыты өседі.Бұл уақытты азайту үшін, АЛҚ жылдам әсер етуін өсіру МС үшін, 564ИП4 жылдам тасмалдайтын сұлбаны қолдану керек. 26, б)сурет.

|

|

|

Төрт МС АЛҚ және бір жылдам тасмалдайтын МС 16 разядты толық параллель АЛҚалуға болады.Оның қосу уақыты бір микросұлбаның қосу уақытына тең.

9лекция. Кодтайтын және декодтайтын құрылғылар. Шифраторлар. Дешифраторлар (декодерлер).

9.1 Шифраторылар

Шифратор (кодер) –кірісіне берілген (кіретін) басқаратын сигналдарды n-разрядты екілік кодқа айналдыруға арналған функциональды түйіншік.

Сонымен қатар, мұндай сигналдар немесе командалар ондық сандар болуы мүмкін, мысалы шифратордың көмегімен екілік кодқа түрленетін командының номері .

Мысал ретінде 3-разрядты шифратордың сұлбасын жасайық. Алдымен сигналдың коды екілік кодпен берілген,кодтар кестесін (ақиқат кестесін) сызайық.(27,а сурет) .НЕМЕСЕ элементерімен іске асырылған сұлба 27,б суретінде көрсетілген.

27сурет. 3-разрядты ширатордың кодтар кестесі. а), оның функциональдық сұлбасы б)және ШГБ в).

Жалпы жағдайда ,екілік кодты қолданғанда 2n кіріс сигналдарын кодтауға болады. Егерде кірісінің біреуіне де жалпы жағдайда кіріс сигналы берілмейтін болса,онда жоғарғыда қаралған сұлбада «000» шығу коды

X0кіріске сигнал бергенде баршығыстар болады. X0сигналын бірмағаналы идентификация жасау үшін, интегралдық сұлбаларда тағы бір сигнал қалыптасады, ол кіріс сигналдың берілуінің белгісі,бұл басқа мақсаттарда да қолданылады.28 суретте 3 разрядты басым (приортетті) 8 кірісі бар шифратордың ШГБ(шарты графикалық белгісі)көрсетілген

28сурет. 3-разрядты басым (приоритетті) шифратор К555ИВ1 а) және екі МС жалғағаны б)

Кез келген кірісіне сигнал берілгенде,G=1, P=0 болып тағайындаладыда, ал цифрлық шығыстарында-сигнал берілген кірістің номерінің екілік коды

шығады. Егерде сигнал біруақытта екі немесе бірнеше кіріске берілсе,онда шығысында үлкен номері бар кірістің коды тағайындалады.Осыдан шифратордың аты басым (приоритетті) деп аталады.

Егер 0…7 кірістерінің біріне сигнал (лог.«0») берілсе, DD3 шығыстарында тура кодтың кіші разрядтары пайда болады, ал G DD1 шығысында- лог. «0», егерде 8…15 кірістерінің біріне лог.«0» берілсе,ондаР кірісінен берілген лог. «1»DD2DD1-ің жұмыс істеуіне тиым салады.Бұл жағдайда DD3кіші разрядтары DD2,микросхемамен анықталады, ал 8 крістің шығысында шығыс коды лог. «1» болады. Сонымен 1, 2, 4, 8шығысынан кіріс сигнал берілген кірістің номеріне сәйкес тура код алуға болады

Дешифраторлар (декодерлар)

n кірістің кіреберісіндегі кодқа тәуелді, тек қана өзінің 2n кірістерінің бірінде «лог. 1»(жоғарғы деңгейдегі дешифратор) немесе «лог. 1» (төменгі деңгейдегі дешифратор) сигналын тудыратын функционалдық түйіншік дешифратор деп аталады.

Дешифратор — функциональный узел, вырабатывающий сигнал «лог. 1» (дешифратор высокого уровня) или сигнал «лог. 0» (дешифратор низкого уровня) только на одном из своих 2n выходах в зависимости от кода двоичного числа на n входах.

29 сурет. Дешифратор: а)ақиқат кестесі; б) – функциональдық сұлба.

Дешифраторлар басқару құрылғыларында кеңінен қолдынылады.Олар кірісіндегі сигналға сәйкес қандай бірорындаушы құрылғыға әсер ететін

басқаратын сигнал қалыптастырады

Дешифраторлардың интегральды микросхемаларды қосымша кірістерімен жасайды, мысалы рұқсат беретін кіріспен (стробтау). Стробтау оның жұмысын кірісіндегі цифрлық код өзгергенде өту үрдісі уақыт интервалында жұмысына тиым салып, кірісінде жалған сигналдардың пайда болдырмайды.

ИД3 (30 сурет) микросхемасының 4адресті кірісі бар1,2,4,8 екілік кодының салмақтық коэффициенті бар, стробтайтын S екі инверсті кіріс,ЖӘНЕ мен біріктірген, және 0–15 дейін 16 инверсті кірісі бар.

Егер стробтаудың екі кірісінде «лог. 0»,онда номері кіріс кодының ондық эквивалентіне сәйкес шығыста «лог. 0» болады.Егерде S стробтайтын кірістердің бірінде «лог. 1» болса, онда микросхемалардыңбарлық шығысында кірістерінің жағдайына байланысыз «лог. 1».қалыптасады.

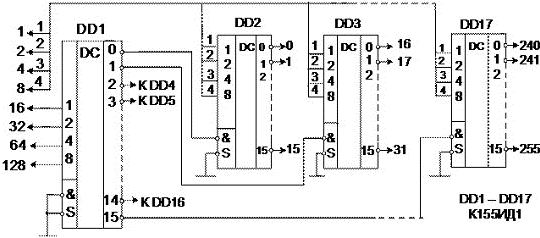

Екі стробтау кірісінің барлығы микросхемалардың қолданылуының мұмкіндігін кеңейтеді. Бір инвертормен толықтырылған ИД3 екі микросхемадан 32 кірісі бар дешифратор(31сурет), жинауға болады, ал 17 микросхемадан-256 кірісі бар дешифраторды(32сурет).

32сурет. 256 шығысы бар дешифратор

10лекция

. Цифрлық сигналдардың коммуторлары. Мультиплексорлар. Дешифраторлар-демультиплексорлар.

9.1Мультиплексорлар

n-адрестік кірісі, N=2nинформациялықкірісі,бір шығысы бар және N кіріс желісінен түсетін шығыс желісіне түсетін информацияны басқарылатын коммутация жасайтын функциональдық түйіншікті мультиплексор дейді. Белгілі кіріс желісін коммутациялау екілік адрестік кодына an-1,…a2,a1,a0сәйкес іске асырылады.

Егерде адрестің коды n разрядты болса,әр бір N кіріс желісін шығыс желісін қосуды қамтамасыз ететін N=2nадрестік сигналдардың комбинацияларын әске асыруға болады.Мұндай мультиплексорды «N-нен бірге» аталады.

Артық адрестік сигналдардың комбинациялары бар болса, кіріс желісініңкез келген N≤2n саны бар мультиплексор жасауға болады. Қарапайым жағдайда екі разрядты адрестық кодта(n=2)шығатын желілердің максималь саны N=2n=4 тең. Мультиплексордың ақиқат кестесі 33,асуретте көрсетілген.

33сурет.4:1 мультиплексорыа) ақиқат кестесі;

б)функциональдық сұлбасы; в)шарты графикалық белгісі.

Ақиқат кестесіне сәйкес жазылған мультиплексордың сипатама теңдеуі мына түрде жазылады:

Мультиплексордың функциональдық сұлбасының құрамына екі инвертор, төрт «ЖӘНЕ»вентилі, және бір «НЕМЕСЕ» вентилі кіретіні алынған теңдеулерден білуге болады. Қазіргі уақытта өндіріс құрамына n=2,3 және 4 адресті кірісі бар мультиплексорлер кіретін МС сериясын шығарады. n=2 тең болғанда қабаталғантөртканалды(2n=4)мультиплексорлердің информациялық кірістердің сигналдарының саны 2n+2n=8.4 каналды қабаталғанстробтайтын К555КП12мультиплксордың шарты графикалық белгісі 34,а суретте келтірілген.

34сурет.Қосақталған 4-каналды мультиплексор К555КП12 а) және оның негіздегі 8-каналды мультиплексор б).

Стробтау кірістері, k2n-информациалық кірістері бар,мұндағы k=2, 3, 4… тең , мультиплексорларды (коммутаторларды) істеуге қолдынылады.Сторбтауы бар,қосақталған 4-каналды 8:1 мультиплексордың сұлбасы 34,б суретте келтірілген.

лог. «0» жәнелог. «1» сәйкес тұрақты деңгейді ақпараттық кірістерге берілсе, онда мультиплексордың шығысында кез келген өзіңе ұнаған басқаратын кодтың айнымалысының функциясын алуға болады.Бірақ бұл жағдайда іске асырылатын шығатын функцияның айнымалыларының саны басқаратын кодтың разрядына тең.

Жалпы жағдайда ақпаратық кірістерге тұрақсыз логикалық деңгейлер беруге болады, сонда мультиплексордың шығысында айнымалысы көп логикалық функция іске асырылады. В общем случае на информационные входы можно подавать не постоянные логические уровни, тогда на выходе мультиплексора реализуется логическая функция с большим числом переменных.

Дата добавления: 2018-02-18; просмотров: 1555; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!