Список рекомендуемой литературы

Тематика – задача 3. Анализ работы цифрового устройства, согласно задания

| Номер варианта | Задание |

| 1. | Двоичные сумматоры: четвертьсумматор, полусумматор. |

| 2. | Одноразрядное устройство для выполненияопераций суммирования и вычитания. |

| 3. | Восьмиразрядный сумматор. |

| 4. | Четырехразрядный вычитатель. |

| 5. | Цифровой компаратор (выполнение операций >,<=,<>) |

| 6. | Цифровой компаратор (выполнение операций <,=,>=) |

| 7. | Устройство контроля чётности. Постройте схему формирования бита чётности для четырёхразрядного кода. |

| 8. | Устройство контроля чётности. Постройте схему формирования бита чётности для пятирёхразрядного кода. |

| 9. | Дешифратор 74154. |

| 10. | Шифратор 74148. |

| 11. | Мультиплексор. Анализ сдвоенного четырехканального мультиплексора (микросхема 74153). |

| 12. | Демультиплексор. Схема работы двухканального демультиплексора. |

| 13. | Триггеры. Реализация и применение RS триггеров. |

| 14. | Триггеры. Реализация и применение JK триггеров. |

| 15. | Триггеры. Реализация и применение T триггеров. |

| 16. | Четрырехразрядный счётчик с последовательным переносом на D-триггерах. |

| 17. | Четрырехразрядный регистр сдвига на D-триггерах. |

Тематика – задача 4. Синтез комбинационного цифрового устройства, согласно задания

Формулировка задачи

1. В последнюю строку таблицы истинности вписать заданное восьмиразрядное двоичное число Y. Представить логическую функцию, заданную таблицей истинности, в СДНФ (СКНФ) и в виде карты Карно.

2. Минимизировать рассматриваемую логическую функцию двумя способами: аналитическим и с помощью карты Карно.

3. Построить схему, реализующую заданную на наборе логических элементов:

- И (AND), ИЛИ (OR), НЕ (NOT).

- И-НЕ (NAND).

- ИЛИ-НЕ (NOR).

4. Постройте реализацию заданной функции с помощью мультиплексора 8х1 с тремя управляющими входами.

Варианты заданий (вариант определяется по номеру в журнале)

| Вариант | Y | Вариант | Y |

| 1 | 01101110 | 16 | 11110001 |

| 2 | 11011100 | 17 | 11100011 |

| 3 | 10111001 | 18 | 11000111 |

| 4 | 01110011 | 19 | 10001111 |

| 5 | 11100110 | 20 | 00011111 |

| 6 | 11001101 | 21 | 00111110 |

| 7 | 10011011 | 22 | 01111100 |

| 8 | 10101110 | 23 | 11110100 |

| 9 | 01011101 | 24 | 11101001 |

| 10 | 10111010 | 25 | 11010011 |

| 11 | 01110101 | 26 | 10100111 |

| 12 | 11101010 | 27 | 01001111 |

| 13 | 11010100 | 28 | 10011110 |

| 14 | 10101001 | 29 | 00111101 |

| 15 | 11111000 | 30 | 01111010 |

Пример выполнения:

Задано Y=00110101

1. Строим таблицу истинности логической функции:

| A | B | C | Y |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

a. Запишем функцию в дизъюнктивной нормальной форме:

Y=A’BC’+A’BC+AB’C+ABC

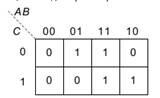

b. Запишем функцию в виде карты Карно:

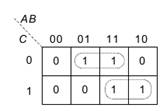

2. Минимизируем логическую функцию с помощью карты Карно:

a. На карте Карно выделяем две группы единиц, расположенных в соседних клетках.

b. Минимизированная логическая функция имеет вид: C =BC’+AC.

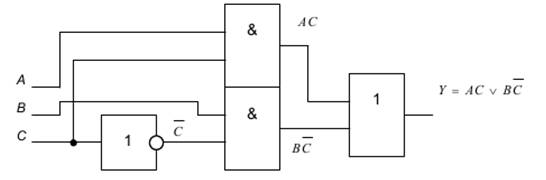

3. Схема на элементах И, ИЛИ, НЕ:

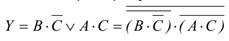

- Схема на элементах И-НЕ:

b. Для построения схемы преобразуем минимизированное логическое уравнение по закону де Моргана:

c. По полученному уравнению строим схему:

- Для построения схемы в базисе ИЛИ-НЕ исходное уравнение также требуется преобразовать, используя закон де Моргана, а затем по полученному уравнению построить схему.

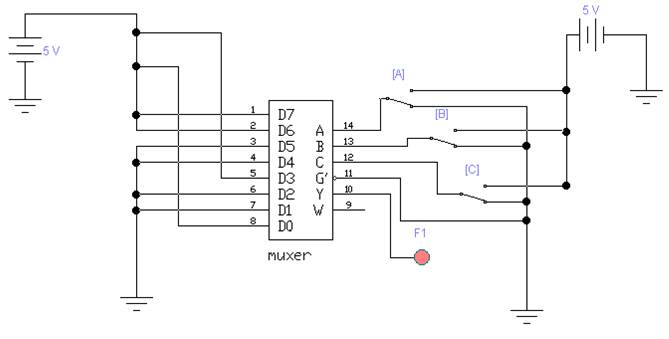

4. Синтез устройства на базе мультиплексора:

a. Определим значение найденной функции для каждой комбинации значений аргументов и заполните графу F1paсч.

| A | B | C | F1paсч | F1рез |

| 0 | 0 | 0 | 1 | |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 1 | |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 0 | |

| 1 | 1 | 1 | 1 |

b. Из таблицы видно, что для реализации функции на мультиплексоре необходимо подать на информационный вход мультиплексора с номером N сигнал, значение которого равно соответствующему значению функции F1, т. е. на входы с номерами 1, 2, 4, 5 следует подать уровень логического нуля, а на остальные - уровень логической единицы. Построим схему.

При помощи ключей А, В, С подаём все возможные комбинации логических сигналов на входы мультиплексора и, определяя уровень сигнала на выходе Y логическим пробником F1, заполняем графу F1рез в таблице.

Вывод: Функция, реализуемая мультиплексором, описывается заданным выражением.

Список рекомендуемой литературы

1. Бойт К. Цифровая электроника. Москва: Техносфера, 2007. - 422с.

2. Вычислительная техника:метод.пособие /авт.-сост.Б.В.Цыбаков.- М.,2004.- 112 с

3. Горнец Н.Н.Организация ЭВМ и систем.-М.:Академия,2008. – 320 с.

4. Гук М. Аппаратные средства IBM PC. – СПб.: Питер, 2006. – 1072с.

5. Келим Ю.М. Вычислительная техника.- М.:Академия,2007.-384 с.

6. Мышляева И.М.Цифровая схемотехника.- М.:Академия,2005.-400 с.

7. Нефёдова Н.В. Карманный справочник по электронике и электротехнике. – Изд. 2-е. – Ростов на Дону: Феникс, 2007. – 283с.

8. Преснухин Л. Н. Расчет элементов цифровых устройств.- М.:Высш.шк.,1991.- 526 с.

9. Управляющие вычислительные комплексы /ред. Н.Л.Прохоров.- М.:Финансы и статистика, 2003.- 352 с.

Дата добавления: 2018-05-12; просмотров: 189; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!