ПОДГОТОВКА УПРАВЛЯЮЩЕЙ ПРОГРАММЫ (УП). ПРОГРАММИРОВАНИЕ ПАРАЛЛЕЛЬНЫХ ВЕТВЕЙ

Исходной информацией для подготовки УП может быть словесное описание алгоритма технологического процесса, блок-схема алгоритма, циклограмма, граф-схема алгоритма, таблица истинности. Удобным исходным материалом является также релейно-контактная схема (если она есть). Необходимо далее выбрать контроллер и ознакомиться с его возможностями, среди которых параметры вх.ивых. сигналов.

Написание программы начинается с инициализации: интерфейса, АЦП, ЦАП, включение специальных контактов – один раз срабатывает, и программа больше не обращается к нему.Далее объявляем переменные.

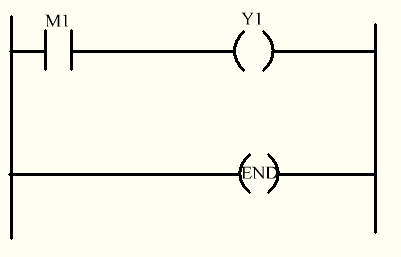

Ветвь всегда начинается с контакта либо условия, далее строка оканчивается реле, и в конце программы END.

Ветвь всегда начинается с контакта либо условия, далее строка оканчивается реле, и в конце программы END.

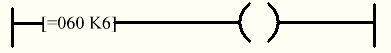

Пример параллельной ветви:

Программа выполняется последовательно строка за строкой.

Программа выполняется последовательно строка за строкой.

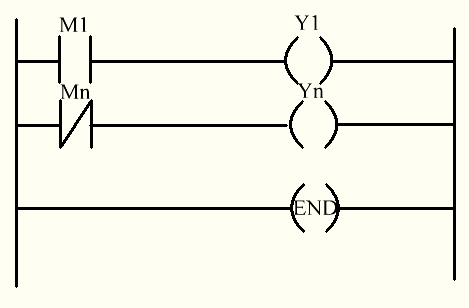

ТРИГГЕР С ПАМЯТЬЮ RS.

Триггер – ячейка памяти, которая в языке LADобъединяетфункции катушек установки и сброса. Вход S (set) – установка, вход R (reset) – катушкесброса. Сигнальное состояние двоичного операнда находитсяна выходе Q функции памяти.

В блочном элементе памяти RS приоритет имеет входустановки (set). Приоритет установки означает, что функцияпамяти остается установленной, если сигналимеется одновременно на входе установки и входе сброса.

Блочные элементы памяти (memoryboxes)

Рис. Функции памяти языка РКС(LAD)

В соответствии с последовательным исполнением инструкций CPU сбрасывает операнд памяти с появлением сигнала сброса, обрабатываемый первым, но затем вновь устанавливает его, когда обрабатывается сигнал установки. Операнд памяти остается установленным, пока обрабатывается остальная программа.

|

|

|

Если операнд памяти является выходом, эта недолговременная установка имеет место только в выходной таблице состояния процесса, а (внешний) выход в соответствующем модуле выхода остается неизменным. CPU не передает выходную таблицу состояния процесса в модули выходов до конца программного цикла.

Приоритет установки при использовании функции для работы с памятьюявляется исключением. Он применяется,к примеру,в реализации буфера сообщений о сбое, если на входе установки постоянное текущее сообщение об ошибке должно продолжить установку функции памяти, несмотря на подтверждение на входе сброса.

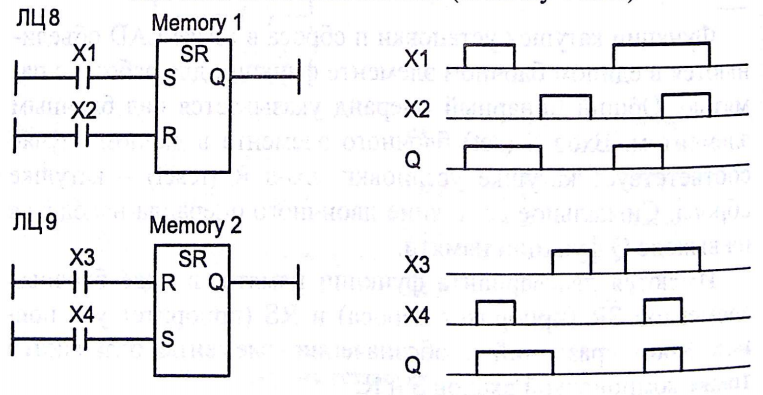

3.6.ПРИСВАИВАНИЕ В FBD.

Логическая схема или логическая операция всегда должна быть завершена оператором, например, присваивания. В результате присваивания бинарный операнд получает значение результата логической операции (RLO).

Логическая схема или логическая операция всегда должна быть завершена оператором, например, присваивания. В результате присваивания бинарный операнд получает значение результата логической операции (RLO).

Блочный элемент присваивания как завершающий элемент цепи присваивает (назначает) результат логической операции непосредственно операнду, соединенному с блочным элементом, как показано ниже.

|

|

|

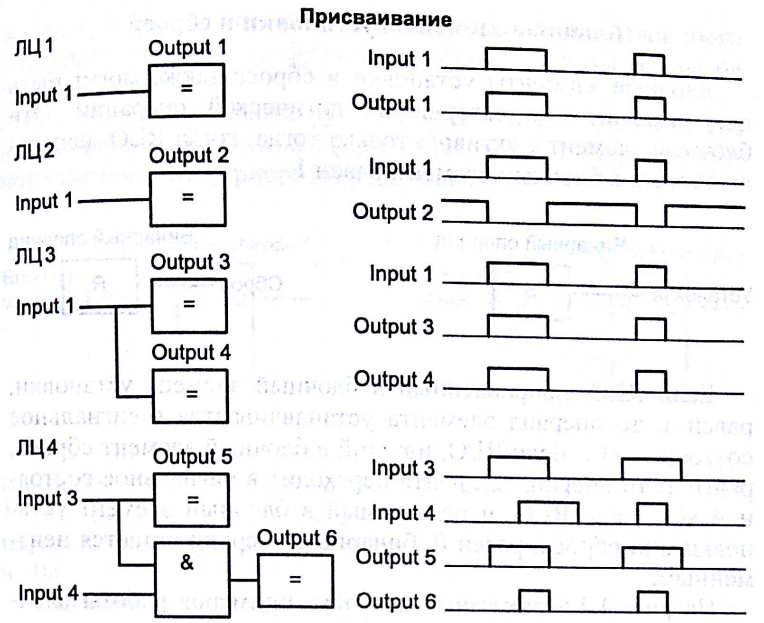

Работу блочного элемента присваивания поясним с помощью рисунка 1.

а): если сигнал на катушке присутствует, то операнд установлен: катушка возбуждена; если сигнала нет, то операнд не установлен (сброшен).

б): с помощью NOT-контакта перед катушкой можно получить инверсное значение операнда

в): несколько катушек можно соединить параллельно (до 16 катушек)

г) можно получать последовательно-параллельные схемы.

Рисунок 1. Присваивание FBD

Дата добавления: 2018-05-12; просмотров: 414; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!