Пример реализации кэш памяти в процессоре i486

КЭШ имеет объем 8Кб и предназначен для хранения данных и команд. Он разделен на 4 сектора. Количество блоков в каждом секторе 128.

Центральный процессор не поддерживает частичного заполнения строк, поэтому все строки кэш должны быть достоверными и полностью заполненными. В блоке данных в каждом секторе содержится информация равная 16-ти последовательным ячейкам, начиная с адреса кратного 16. При заполнении КЭШ используется пакетный режим передачи данных. Длина строки КЭШ должна составлять 16 байт.

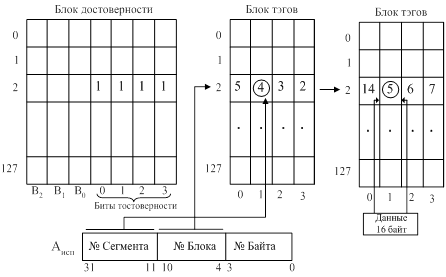

Блок тегов тоже разделен на 4 сектора, в каждом секторе 128 блоков. Каждый тэг содержит номер отображаемого сегмента.

В блоке достоверности младшие 4 бита (0..3) определяют строку как достоверную, а 4..7 биты следят за использованием данных. Разряды 4..7 используются при реализации алгоритма LRU.

Адресация КЭШ осуществляется путем разделения старших 128 бит физического адреса на две части. Старшие 21 бит служат полем тега(указывают номер сегмента) и применяются для различения кэшированных данных из любой другой 16-байтной строки, которая может находиться в том же блоке.

Младшие 7 бит образуют поле блока и определяют множество, в котором могут храниться данные. Биты с 0 по 3 определяют номер отображенного байта в строке кэша.

В качестве алгоритма замещения LRU используется приближенная реализация алгоритма - “двоичное дерево”.

Обозначим сектора кэш памяти: S0, S1, S2, S3. Каждым двум секторам ставится в соответствие триггер. При обращении к сектору формируется 3-х разрядный двоичный код (B2 B1B0 ). Этот код модифицируется при каждом попадании. Если произошло обращение к верхней группе блока, то соответствующий триггер устанавливается в 1, если же к нижней, то триггер устанавливается в 0. Выбор заменяемого сектора определяется по значению B0, B1, B2 в соответствии с таблицей.

|

|

|

Дата добавления: 2015-12-17; просмотров: 76; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!