Signal _ name ' attribute _ name

Обратим особое внимание на атрибуты (delayed, stable, quiet, transaction), значениями которых являются сигналы. Эти атрибуты создают новые сигналы в модели.

Перечень предопределенных в языке VHDL атрибутов сигналов (где s — имя сигнала).

| Название атрибута | Описание |

| S'delayed(T) | Сигнал, имеет то же значение, что и S, но задержанное на время Т (если значение задержки не задано, то принимается дельта-задержка) |

| S'stable(T) | Сигнал, имеет значение true, если в течение времени Т сигнал не изменялся |

| S'quiet(T) | Сигнал, имеет значение true, если в течение времени Т к сигналу не было обращений |

| S ' transaction | Сигнал типа bit , переключается из "0" в "1" (или, наоборот) при каждом обращении к S |

| S ' event | Принимает значение true, если в текущем цикле моделирования происходило изменение сигнала |

| S ' active | Принимает значение true, если в текущем цикле моделирования есть обращение к этому сигналу |

| S ' last_event | Интервал времени, прошедший с последнего изменения сигнала |

| S ' last_active | Интервал времени, прошедший с последнего обращения к этому сигналу |

| S ' last_value | Предыдущее значение сигнала |

РАЗЛИЧИЕ МЕЖДУ СИГНАЛАМИ И ПЕРЕМЕННЫМИ ЯЗЫКА VHDL

Любой проект является описанием явлений в дискретных системах. Эти явления могут представляться тремя различными категориями данных: константы, переменные и сигналы. signal — это информация, передаваемая между модулями проекта или представляющая входные и выходные данные проектируемого устройства. Сигналу присваиваются свойства изменения во времени. variable — это вспомогательная информационная единица, используемая для описания внутренних операций в программных блоках. Присвоение значения сигналу отображается знаком <=, а переменной – знаком :=.

В языке VHDL введены два типа операторов — последовательные и параллельные.Последовательные операторы выполняются последовательно друг за другом в порядке записи (оператор присваивания переменной, оператор присваивания сигналу, условные операторы, оператор выбора и ряд других).

Исполнение параллельных операторовинициируется по событийному принципу, т. е. они исполняются тогда, когда реализация других операторов программы создала условия для их исполнения. Параллельные операторы представляют части алгоритма, которые в реальной системе могут исполняться одновременно.

Присвоения сигналу существенно отличается от присвоения переменной. Присвоение сигналу не приводит непосредственно к изменению его значения. Новое значение сначала заносится в буфер, называемый драйвером сигнала, и следующие операторы в теле процесса оперируют со старыми значениями. Фактическое изменение значения сигнала выполняется только после исполнения до конца процессов и других параллельных операторов, инициированных общим событием, или после исполнения оператора останова wait.

Наиболее существенные различия сигналов и переменных.

1. Переменные меняют значения сразу после присвоения, и новые значения непосредственно учитываются во всех преобразованиях, записанных в теле процесса после такого присвоения.

2. Значение сигнала меняется не сразу после выполнения присвоения. Передача значения сигналу может быть еще более задержана, если оператор присваивания содержит выражение задержки after.

3. Переменная определена только внутри тела процесса, сигнал — во всем архитектурном теле.

4. Переменной можно переприсваивать значение в теле процесса. Сигнал внутри одного процесса может иметь только один драйвер. То есть присвоение значения сигналу может быть выполнено только один раз в теле.

ОПЕРАТОР УСЛОВНОГО ПРИСВОЕНИЯ ЗНАЧЕНИЯ СИГНАЛУ НА ЯЗЫКЕ VHDL

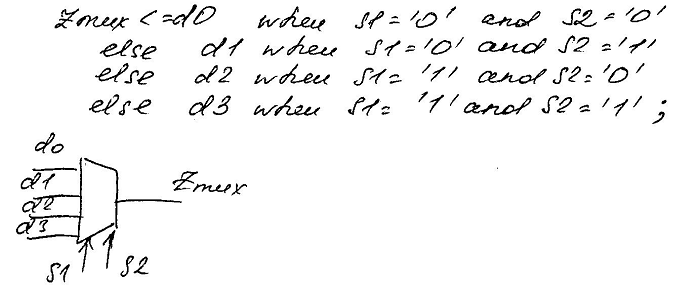

Оператор условного присваивания имеет следующий синтаксис:

имя_сигнала <= [механизм задержки] {значение when условие else }

значение [ when условие];

Этот оператор позволяет определить, которая из форм, в зависимости от значений логических условий, будет присвоена сигналу. Примеры приведены в листингах ниже.

Пример 1

zmux: z<=d0 when sell='0' and sel0='0' else

dl when sell-'0' and sel0='l' else

d2 when sell='l' and sel0='0' else

d3 when sell='l' and sel0='l';

Пример 2

zmux: process

begin

if sell='0' and sel0='0' then z<=d0

elsif sell='0' and sel0='l' then z<=dl

elsif sell='l' and sel0='0' then z<=d2

elsif sell='1' and selO='l' then z<=d3

end if;

wait on d0,dl,d2,d3,sel0,sell;

end process zmux;

Во втором примере список чувствительности для процесса отсутствует. Вместо него используется конструкция wait on с последующим списком сигналов. Это работает следующим образом: процесс выполняется один раз до этой секции, далее он приостанавливается, пока не произойдет изменение какого-либо из сигналов в списке чувствительности, а затем процесс выполняется сначала.

В записи оператора условного присваивания имеет значение порядок записи специфицируемых условий. Условия вычисляются и проверяются в том порядке, в каком они записаны в операторе. Срабатывает первое же из условий, для которого обнаружено истинное значение, и на выход будет передано соответствующее ему значение.

Дата добавления: 2020-04-08; просмотров: 195; Мы поможем в написании вашей работы! |

Мы поможем в написании ваших работ!